Geothermal Technologies Office 2017 Peer Review

Energy Efficiency & Renewable Energy

### Enhanced High Temperature/High Speed Data Link for Logging Cables

Project Officer: Lauren Boyd Total Project Funding: \$178k + 284k November 15, 2017

#### Avery "Zack" Cashion Sandia National Laboratories EGS Tools

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

This presentation does not contain any proprietary confidential, or otherwise restricted information.

# Relevance to Industry Needs and GTO Objectives

Energy Efficiency & Renewable Energy

### Background

-Increased need for high bandwidth data transmission

- New generation of sensors

- Increased sample rate and accuracy

- Physical logging speed economics (feet/hour)

- -Uplink bottleneck

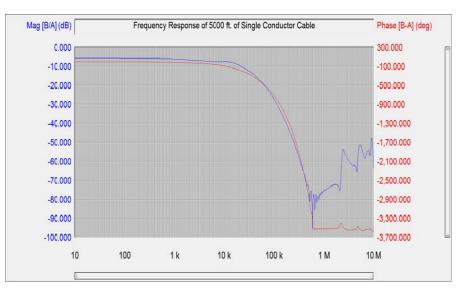

- Poor signal characteristics of high-temperature (HT) wirelines

- -Currently single conductor data rates are limited to ~200 kbps w/ some reports of ~500kbps

### •Goals

- Enable high transmission rate of raw data from downhole tools

Acoustic logging, seismic measurements

- -Develop an asymmetric HT high-speed (HS) data link system

- Uplink data rates >1Mbps over 5,000 ft of single-conductor wireline

- Downlink data rates sufficient for command and control

- ■Temperatures up to 210°C

This project has accomplished a data rate of 3.8 Mbps over a 5,000 ft, single conductor wireline with an error rate (BER) of <1e-7 using modern telecommunications techniques.

# Relevance to Industry Needs and GTO Objectives

- Limitations of HT single conductor wirelines

- Designed for tension, temperature, corrosive environment, power transmission

- Not designed for data transmission

- Limitations of HT electronics

- Lack of necessary components

- Low processing speed

- Variability in temperature ratings

- > Appropriate use of bandwidth

- Must maximize available bandwidth to maximize performance

U.S. DEPARTMENT OF

Energy Efficiency & Renewable Energy

# Relevance to Industry Needs and GTO Objectives

- Short Cable Protocols (1Mbps 6Gbps)

- UART, USB, SPI, I<sup>2</sup>C, GPIB, PCI, SATA, FireWire, etc.: Logic level or low level differential

- Medium Length Cable Protocols

- RS232 (~15 m, 20kbps): Higher voltage single ended serial

- Ethernet (~100 m, 10Mbps 10Gbps): Pulse Amplitude Modulation (PAM)

#### Longer cable protocols

- RS485 (~4000 ft), RS422 (~4000 ft): Differential serial

- RS485 can achieve 3.8Mbps at a maximum length of ~100 ft and ~100kbps @ 4000 ft.

- DSL (~18000 ft), Digital TV : Sinusoid Modulation

- Carrier Wave Communications

- AM, FM, LTE, DSL, ASK, FSK, PSK, OOK, QAM, OFDM, etc.

Energy Efficiency &

**Renewable Energy**

U.B. DEPARTMENT OF

Conrad Schlumberger (1912) developing first wireline tool concept. Analog current injection. http://www.slb.com/about/history.aspx

**Note:** Fiber Optics can achieve Gbps data rates over many km of cable and applications for downhole tools will continue to grow in the future. However, there are still important technical and economic hurdles to it becoming applicable in extreme environments. Additionally, fiber communications still must interface electronics to accomplish many advanced communication protocols.

## Methods/Approach

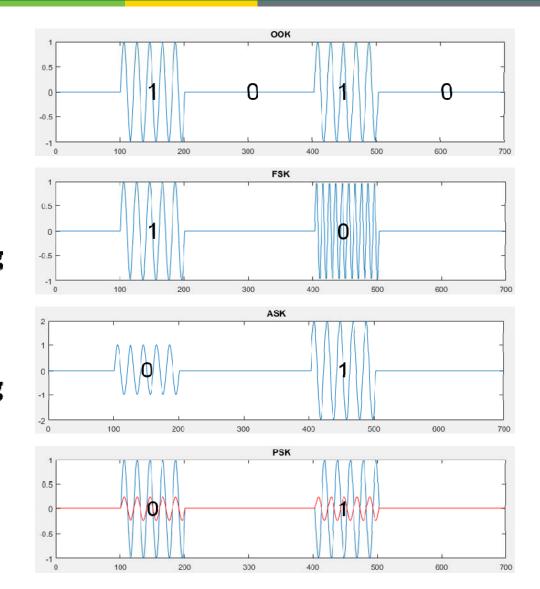

- OOK

On Off Keying

- FSK

Frequency Shift Keying

- ASK

Amplitude Shift Keying

- PSK

Phase Shift Keying

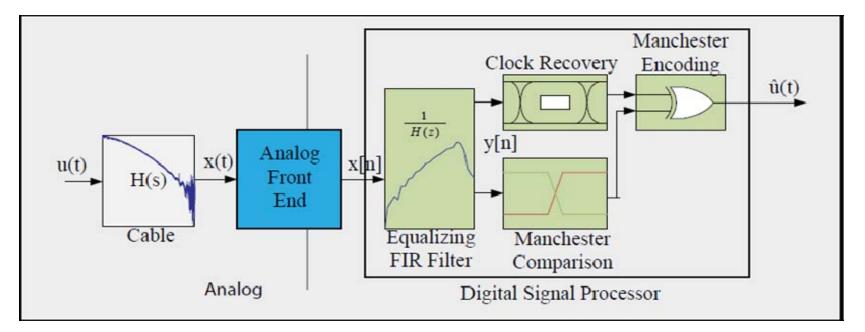

### •Phase 1

Use Manchester encoding (special case of BPSK) in combination with equalizing filter uphole to mitigate wireline distortion

Does not require complicated downhole electronics

Data is xor-ed with clock

-Equalizing filter is difficult to design and computationally intensive

U.8. DEPARTMENT OF

Energy Efficiency & Renewable Energy

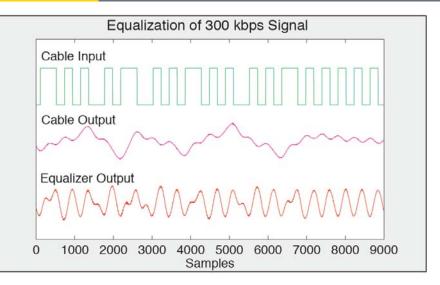

Phase 1 Results

•The equalizer was implemented on a Altera Cyclone III Field Programmable Gate Array (FPGA) using a 720 tap finite impulse response (FIR) filter

-25MHz sampling rate

•The clock and data recovery block, which is also implemented in the Cyclone III FPGA, works to take the equalizer output and convert it back into digital clock and data signals

•The system uses a correlator to recover the data signal and a first order PLL to recover the clock

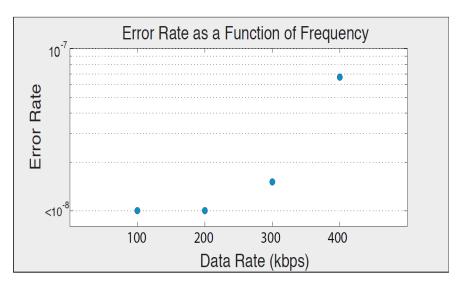

•Maximum data rate achieved is 400kbps with very low error rate

•Fulfilled the objectives of phase 1

•Phase 1 lessons

-The phase 1 approach did not allow to increase speed much beyond 400kbps

Increased error rate and difficulty with PLL locking on for clock recovery

-Inefficient use of bandwidth by Manchester code

•Phase 2 approach

-New approach leverages methods developed by telecom industry

DSL, LTE..

QAM – Quadrature Amplitude Modulation

OFDM – Orthogonal Frequency Division Multiplexing

-Increased requirements for downhole electronics

-Simplified uphole electronics

-Goal to reach speeds >1Mbps

## Methods/Approach

U.8. DEPARTMENT OF

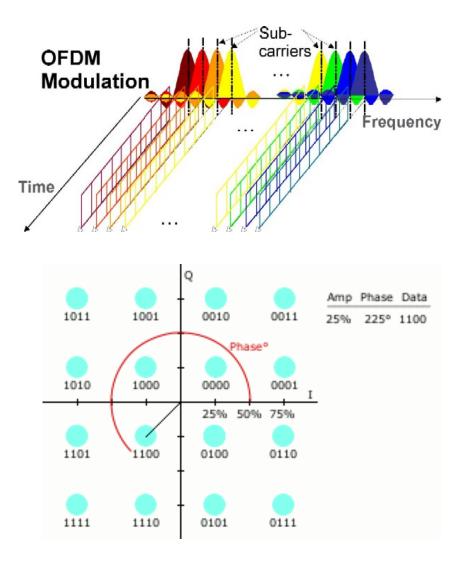

•OFDM – Orthogonal frequency division multiplexing

-Divides the available bandwidth in to multiple narrow band channels

-Computationally intensive - FFT -Efficient use of bandwidth

•QAM – Quadrature Amplitude Modulation

-Each channel uses QAM to encode the data

-The data is encoded by changing the amplitude and phase of a sinusoid

•Compensates for channel distortions

•Sensitive to clock mismatch

U.B. DEPARTMENT OF

Energy Efficiency & Renewable Energy

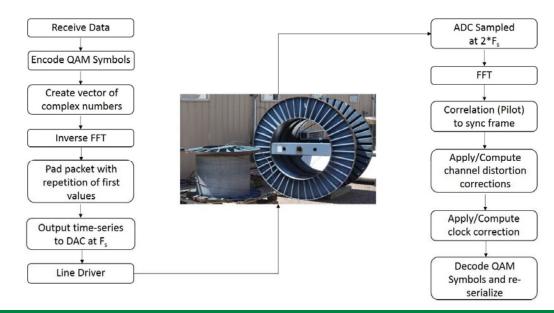

#### **QAM+OFDM Adaptation for HT wireline**

Hardware

Protocol

ENERGY Energy Efficiency & Renewable Energy

- *Packet:* Composite signal consisting of QAM encoded data on all available OFDM channels

- 4 channel example:

iFFT $(A_1e^{i\theta_1}, A_2e^{i\theta_2}, A_3e^{i\theta_3}, A_4e^{i\theta_4}, A_4e^{-i\theta_4}, A_3e^{-i\theta_3}, A_2e^{-i\theta_2}, A_1e^{-i\theta_1})$

Creates a time-series with four frequencies

- $f_1$ : Carries amplitude  $A_1$  and phase  $\theta_1$

- $f_2$ : Carries amplitude  $A_2$  and phase  $\theta_2$

- $f_3$ : Carries amplitude  $A_3$  and phase  $\theta_3$

- $f_4$ : Carries amplitude  $A_4$  and phase  $\theta_4$

ENERGY Ren

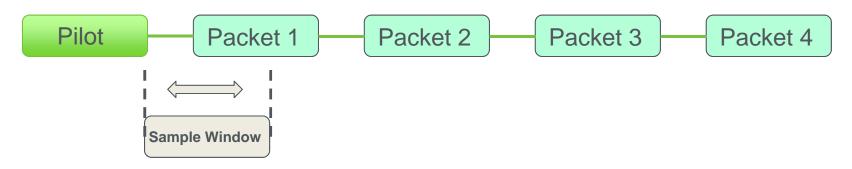

- Frame: Sequence of packets starting with a pilot packet

- A correlation function with the known pilot peaks when the sample window is aligned with the frame pilot

• An FFT of the pilot gives amplitude  $(A_{rec})$  and phase  $(\Theta_{rec})$  values at each frequency in the form of a single complex number  $(A_{rec}e^{i\Theta_{rec}})$ .

Correction Factor =

$$\frac{A_k e^{i\theta_k}}{A_{rec} e^{i\theta_{rec}}} = \left(\frac{A_k}{A_{rec}}\right) e^{i(\theta_k - \theta_{rec})}$$

U.S. DEPARTMENT OF

Energy Efficiency & Renewable Energy

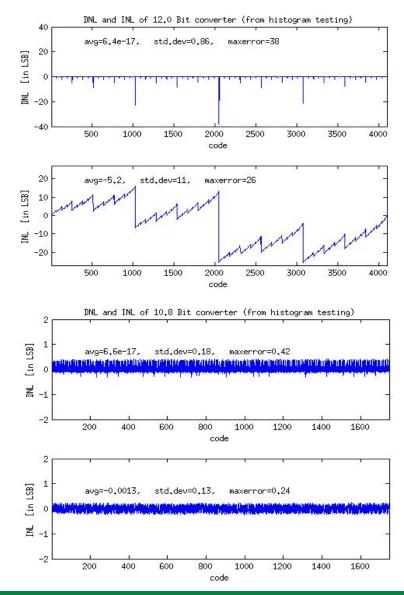

HT digital to analog converter •No commercial part available •Adopted classical R2R ladder approach •Required precision of ~10 bits initial size 12 bits

- •Linearity problems

- -Resistor mismatches

- -Resistor values

- -Achievable rate

- •Developed a linearizing algorithm

- -Sacrifices some bits to linearize output

- 10.8 bit DAC with max DNL of 0.42 LSB and max INL of 0.23 LSB

Precision can be increased further by

increasing initial size of the DAC

Energy Efficiency & Renewable Energy

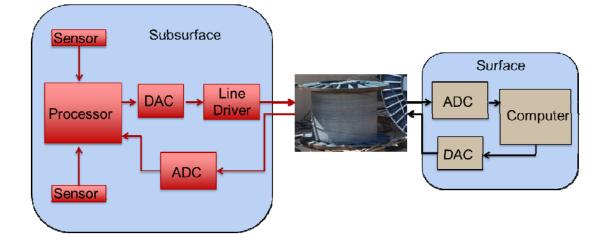

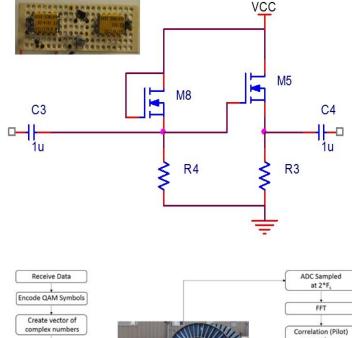

### Developed prototype system

- Downhole: TI DSP, custom DAC and custom line driver

- Uphole: programmable analog filter, NI hardware and a laptop with Matlab

- Power can be delivered simultaneously over the same cable

### Preliminary Results

- Observed speeds up to 3.8 Mbps over 5000ft of wireline

- Link Protocol developed to increase data rate

- Protocol automatically decreases speed to decrease error rate

| Original Planned Milestone/<br>Technical Accomplishment                                                                                                                                                                                                                                                                                               | Actual Milestone/Technical<br>Accomplishment                                                                                                                                                            | Date<br>Completed                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| FY(14) Select HT components (FPGA/processor,<br>precisely matched resistors for DAC, op-amps<br>and transistors for analog line driver) for<br>construction of the downhole transceiver.<br>Develop a robust link protocol capable of<br>adjusting link parameters to changes in cable<br>conditions and mitigating occasional transmission<br>errors | Developed suitable DAC and line driver, HT processor selection has changed based on available components                                                                                                | 09/2014 with<br>advancements on-<br>going |

| FY(14) Develop and test uphole and HT downhole<br>transceivers capable of transmitting data at 1<br>Mbps over 5,000 feet of single conductor wireline<br>using spread spectrum techniques                                                                                                                                                             | Constructed benchtop uphole and HT downhole prototype capable of transmitting data at >1Mbps                                                                                                            | 09/2014                                   |

| FY(15) Improve link protocol to optimize transfer rate while minimizing error on each frequency channel                                                                                                                                                                                                                                               | The link protocol was improved to achieve 3.8Mbps with a bit error rate of <1e-7                                                                                                                        | 09/2015 with<br>advancements on-<br>going |

| FY(17) Begin implementation of downhole communication protocol on high temperature processor                                                                                                                                                                                                                                                          | The most critical mathematical function, the FFT was implemented in fixed point math on a recently developed 300°C microcontroller. With this functionality, the remainder of the protocol is possible. | 09/2017 with<br>advancements on-<br>going |

| 15   US DOE Geothermal Office                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                         | eere.energy                               |

## Research Collaboration and Technology Transfer

ENERGY Energy Efficiency & Renewable Energy

- Initial (Phase 1) collaboration with Harvey Mudd College.

Collaboration ended after phase 1 was completed.

- Presentation at the 2017 High Temperature Electronics Network (Cambridge, UK) led to potential collaboration with high temperature component manufacturers. Collaborative proposals likely.

- Discussion at GRC led to potential testing with established tool manufacturers in need of higher data rates.

### **Future Directions**

| Milestone or Go/No-Go                                                                                                    | Status & Expected Completion Date                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Complete implementation of downhole link protocol on high temperature processor                                          | (01/2018)<br>With the simplified FFT already implemented in fixed point,<br>the protocol can be adapted for any HT processor without<br>an FPU.                              |

| Compare performance of link protocol on all 4 processors currently available for >220°C                                  | (03/2018)<br>Once the protocol is implemented on one HT processor,<br>porting to the other options should be simple                                                          |

| Create hardware/firmware/software modules integrating the HT processor, line driver, DAC, and ADC and test over wireline | (09/2018)<br>A suitable DAC and line driver have been developed and a<br>suitable ADC identified. When the processor selection is<br>complete, the module can be integrated. |

| Work with organizations to develop system<br>into a downhole deployable tool and field test<br>in a geothermal well      | (Future)<br>Interested companies who require higher data rates have<br>been identified and would like to participate in funding<br>proposals                                 |

•Enable high transmission rate of raw data from downhole tools –Acoustic logging, seismic measurements

### •Phase 1

-Employed Manchester encoding and uphole equalizing filter to achieve rates up to 400kbps.

-Not scalable to higher bitrates

### •Phase 2

-Developed prototype HT HS data link system employing OFDM

- Developed custom DAC

- Developed custom line driver

-Observed data rates up to 3.8Mbps over 5000 ft of single-conductor wireline -Temperatures up to 250°C for components evaluated