#

# DOE Office of Electricity TRAC Peer Review

## **SSPS 1.0: Hardware Development**

Smart Universal Power Electronics Regulators (SUPERs) & Intelligent Power Stages (IPSs) for SSPS 1.0

PRINCIPAL INVESTIGATOR

Dr. Madhu Chinthavali,

Leader – Power Electronics Systems Integration (PESI) Group, Distinguished R&D Staff Professional, ORNL

## **PROJECT SUMMARY**

## Demonstration of advanced and standardized power electronics interfaces (SUPER & IPS) for the grid

- □ Universal design for grid interfaces Interfaces that can be tied to assets or loads with changes only to the software layer

- □ Grid interfaces with advanced & intelligent features Autonomous operation, online health monitoring & decision-making capability

- Scalable and interoperable design with standardized interfaces

- □ IPSs with advanced sensing techniques, algorithms capable of estimating the health of at least 2 components

# The Numbers

## DOE PROGRAM OFFICE: **OE** – Transformer Resilience and **Advanced Components (TRAC)**

FUNDING OPPORTUNITY: AOP

LOCATION: **Knoxville**, **Tennessee**

**PROJECT TERM:** 07/01/2020 to 09/30/2022

**PROJECT STATUS:** Ongoing

AWARD AMOUNT (DOE CONTRIBUTION): \$9,000,000

AWARDEE CONTRIBUTION (COST SHARE): **\$0**

**PARTNERS**: **Consortium of University Partners**

# Team - ORNL

ORNL - SUPER architecture, functionalities & advanced algorithms, IPS (developed by ORNL), integration of IPSs from partners

Madhu Chinthavali **Power Electronics System** Architecture

**Brian Rowden** Hardware design and prototyping

Steven Campbell System Integration & Testing

**Jonathan Harter** Hardware development

Radha Sree Krishna Moorthy Project Lead & Software framework development

**Aswad Adib** SUPER and IPS simulation

**Rafal Wojda Magnetics Design**

Jang Euk **Fiber Optic Interface Development**

# University Partners – Library of IPSs

- The Ohio State University, Columbus, Ohio: Dr. Jin Wang

- Virginia Polytechnic Institute and State University (Vtech), Blacksburg, Virginia: Dr. Rolando Burgos

- Florida State University (FSU), Tallahassee, Florida: Dr. Helen Li

- The University of Texas at Austin, Texas: Dr. Alex Huang

- The University of Arkansas (UARK), Fayetteville, Arkansas: Dr. Yue Zhao

- The State University of New York (SUNY) at Stony Brook, New York: Dr. Fang Luo

- The University of North Carolina at Charlotte (UNCC), North Carolina: Dr. Babak Parkhideh

## 14 Professors/PIs, 6 Postdocs, 26 Students

**UNCCHARLOTTE**

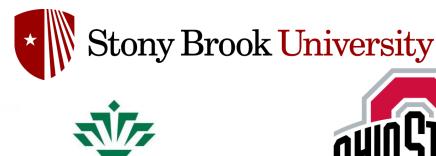

# Innovation: SSPS 1.0 Implementation

- □ SSPS Hubs & Nodes An autonomous grid entity capable of power and information exchange serving as an interface between the grid and end user.

- □ SSPS concept will enable hierarchical control, communication, optimization, protection and intelligence

- Architecture realized by fundamental building blocks – modular, interoperable, scalable, autonomous & intelligent grid tied systems

\*\* "Solid state power substation Technology Roadmap", U. S DOE Office of Electricity, Transformer Resilience and Advanced Components (TRAC) Program, Jun. 2020.

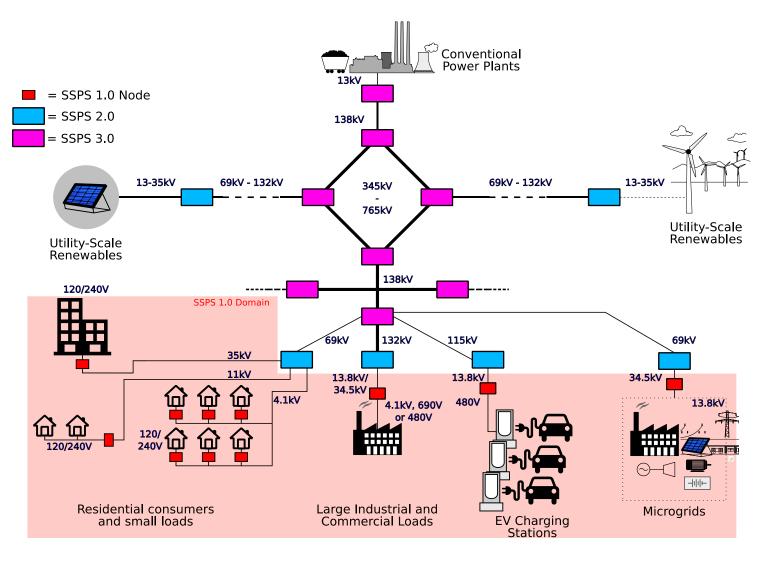

# Innovation: SUPER

State of the Art

**SUPER**

SUPER

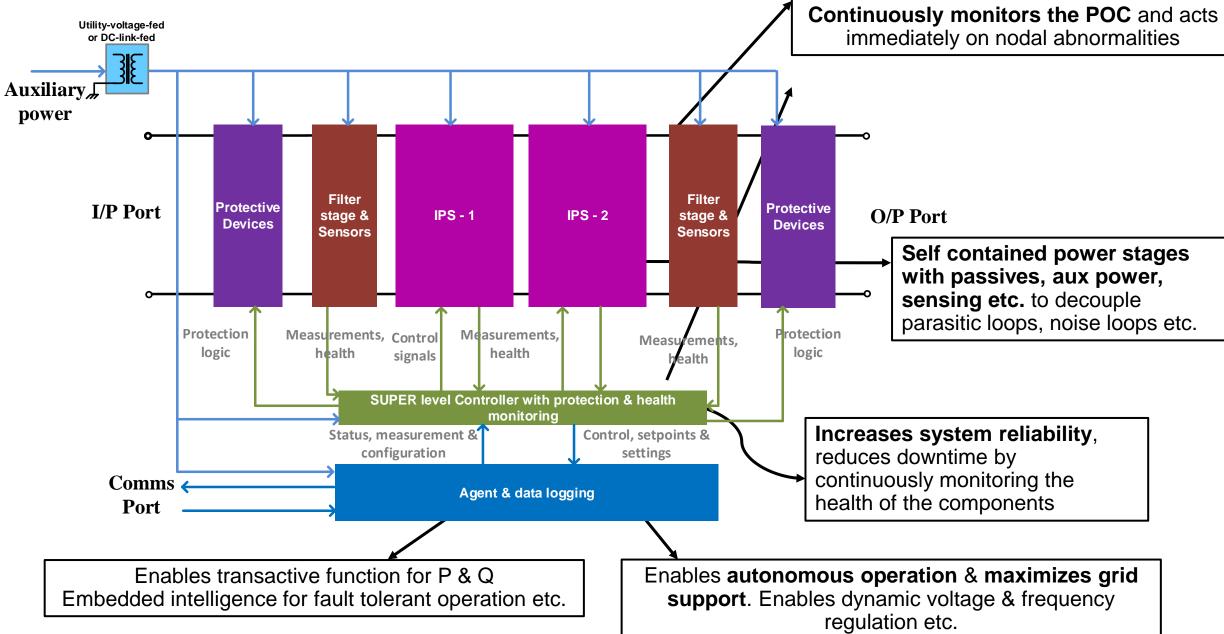

## System level impact

- Easy integration & reduction in BOS costs

- Improved voltage profile at the point of connection (POC)

- De-rated/continuous operation during failure events

- Allows maintenances to be pre- planned

- Can prevent the loss of the inverter from affecting the overall system

- Increases lifetime

- Data for offline learning algorithms

- Improved protection against cyber threats

- Decouples parasitics and noise loops

- Additional sensing & processor can be utilized for internal health monitoring of IPS

8

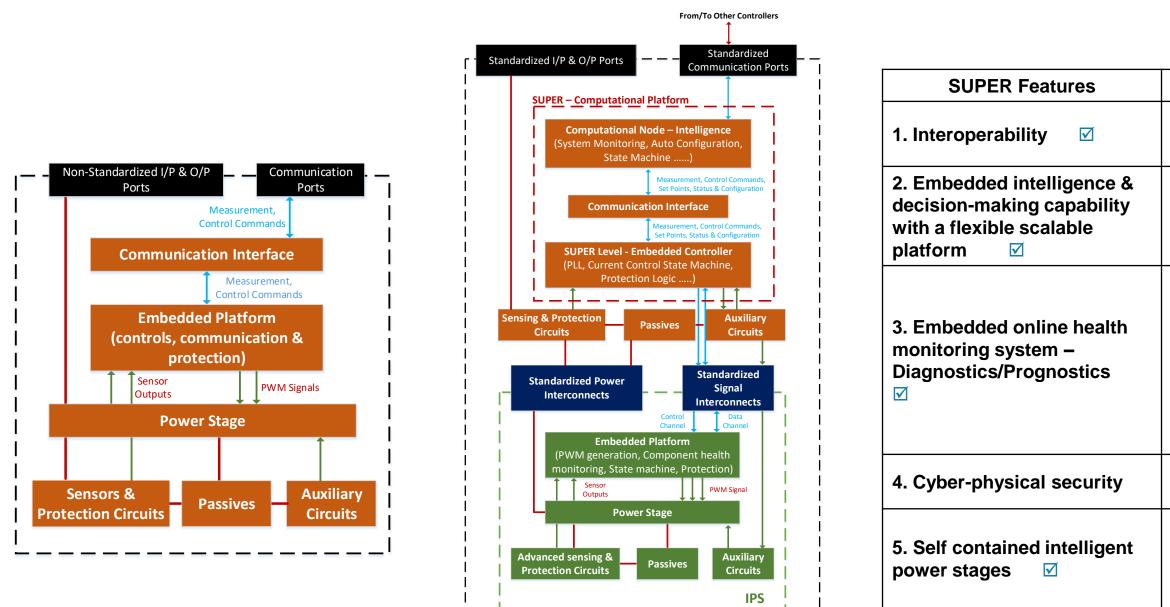

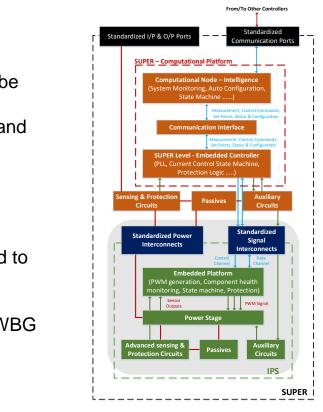

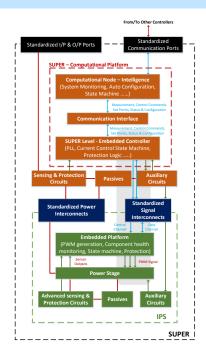

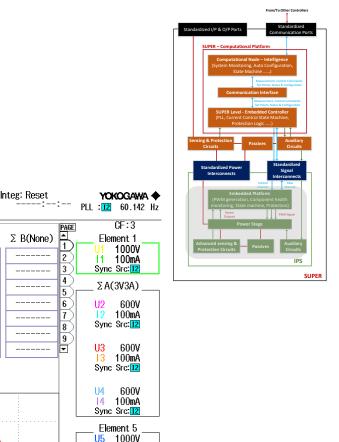

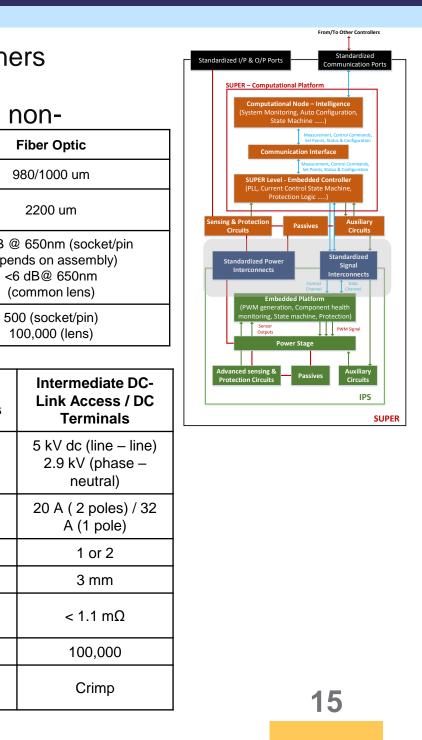

# Innovation: Fundamental Building Blocks - SUPER

Smart Universal Power Electronics Regulators (SUPERs) – Modular, interoperable entities that are for fundamental blocks of SSPS

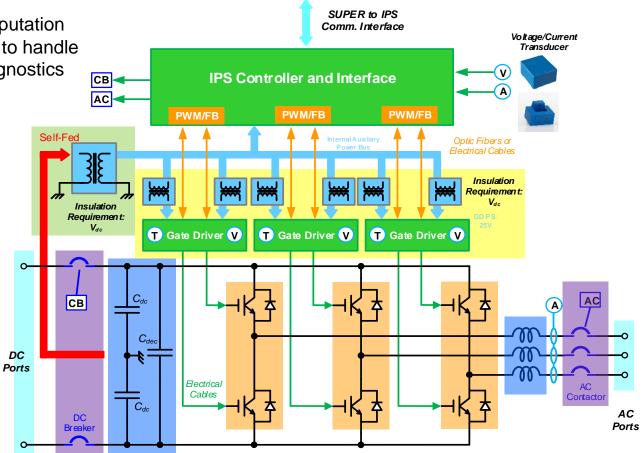

# Innovation – Fundamental Building Blocks – IPS

**Controller:** More powerful computation and communication capability to handle data processing to enable diagnostics and prognostics

## Auxiliary power supply:

Self-maintained power supply provides safe shut-down during system crash and minimize the Interconnection between SUPER and IPS

### Integrated passives:

Ensure safe and reliable performance with the minimum required parameters, so the

**Device:** Advantage packaging to shrink overall SUPER and IPS form factor

**IPS Critical Features Desired by SUPER:**

- Interoperable plug-and-play power stage

- Provide sufficient component-level status information to enable accurate SUPER-level diagnostics and prognostics

Sensors: Several sensors can be integrated into gate drivers to improve the overall form factor and mitigate noise interference

Interconnectors between components within IPS: More optical interconnections involved to improve the noise immunity capability, especially at higher switching frequency of utilized WBG devices

Gate driver: Integrated and intelligent gate driver (i2GD) enables integrated sensing (e.g., dc link voltage, device or phase current), active gate driving, and initially enable diagnostics and prognostics features for SUPER

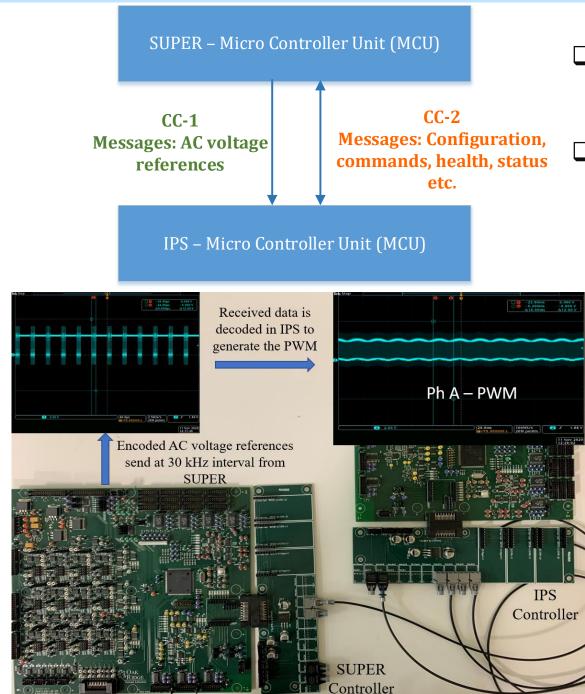

# Innovation Update #1: Communication Validation

- Validation of SUPER & IPS control architecture with a high-speed communication link (6.25 Mbps)

- The communication architecture was validated by all partners

CHIL Setup for SUPER validation in Grid-C

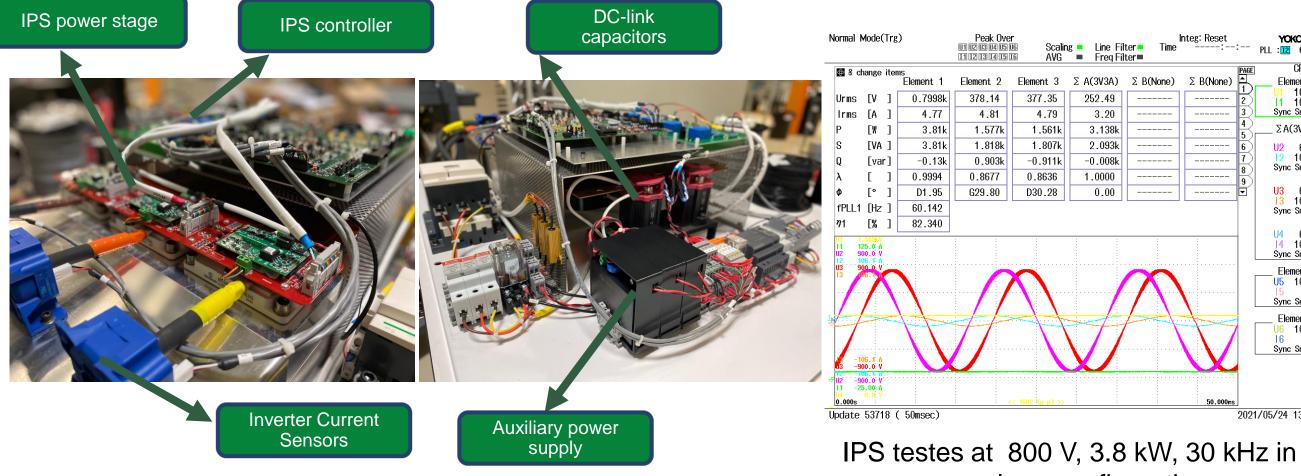

# Innovation Update #2: Baseline IPS Validation

Components of the baseline IPS including contactors, gate drivers, IPS controller, communication expansion board were tested extensively during integration

open loop configuration

Sync Src: 🖪 Element 6 U6 1000V |6 5A Sync\_Src:16

2021/05/24 13:38:21

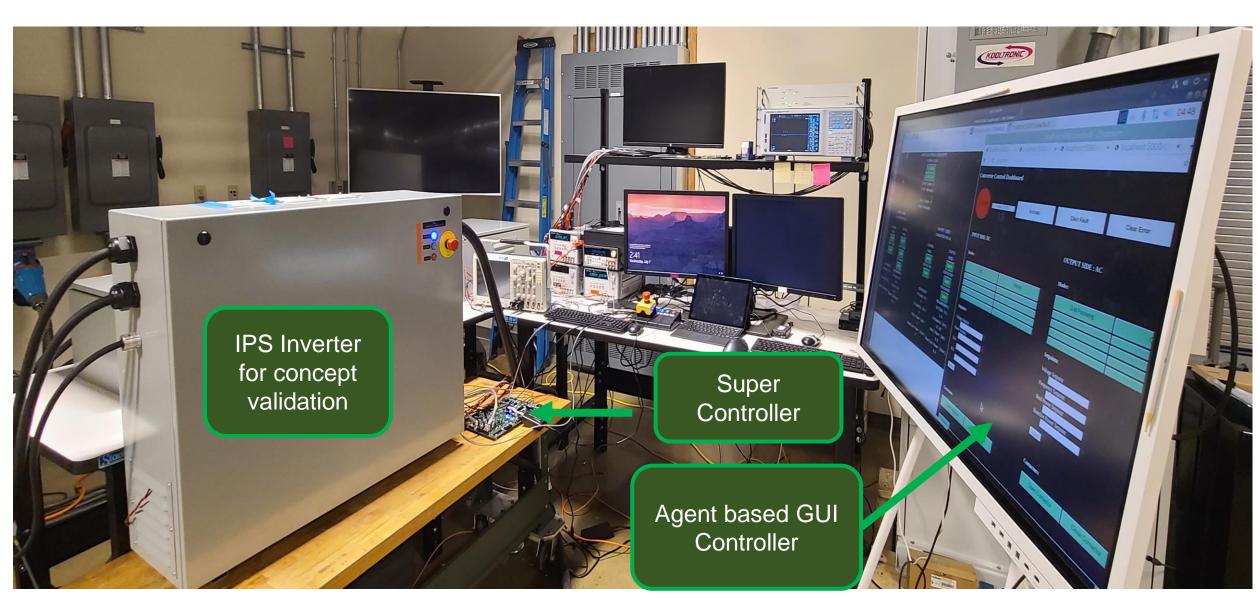

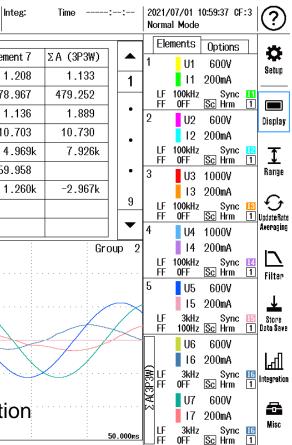

# Innovation Update #3: Overall Architecture Validation

Validation of SUPER & IPS architecture with high-speed communication links, controls, protection and standardized interfaces for grid functions

## Innovation Update #2: Overall Architecture Validation

□ Vdc regulation (GI): The SUPER maintained the dc-link at 1-kV & real power P (up to 15 kW), was injected/absorbed using battery test system

□ P/Q Compensation (DCSI): SUPER injected/absorbed P/Q from/to the grid (Tested up to 10 kW & -5 kVAR)

| 24 JUNE 2021              |                  |      | ) U2 U3 U4 U5 U6<br>) 12 13 14 15 16  |           | Update    | 18771 ( 50ms) | SP Integ: | Time      | ::       | 2021/07/01 12:21:45 CF:3                                                                                                                                                                    | 24 JUNE 2021                                                                                                  | Peak U1U2U3U4U5U<br>Over I1I2I3I4I5I  |           | Update    | 51288(50ms)S | P Int  |

|---------------------------|------------------|------|---------------------------------------|-----------|-----------|---------------|-----------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------|-----------|--------------|--------|

|                           |                  | -    | _                                     | Element 4 | Element 5 | Element 6     | Element 7 | ΣA (3P3₩) |          | Elements     Options       1     U1                                                                                                                                                         |                                                                                                               |                                       | Element 4 | Element 5 | Element 6    | Eleme  |

| Udc [V                    | ]                |      |                                       | 0.99785k  | 0.252     | 1.231         | 0.922     | 1.076     | 1        | 1 U1 600V Setup<br>I1 200mA                                                                                                                                                                 | Udc [V ]                                                                                                      |                                       | 1.00002k  | 0.091     | 1.059        | 1.     |

| Urms [V                   | ]                |      |                                       | 0.99811k  | 479.290   | 479.140       | 478.759   | 478.950   | <b>⊢</b> | LF 100kHz Sync II                                                                                                                                                                           | Urms [V ]                                                                                                     |                                       | 1.00005k  | 479.561   | 479.536      | 478.   |

| Idc [A                    | ]                |      |                                       | -13.681   | 0.004     | 9.659         | -10.541   | -0.441    | •        | FF OFF Sc Hrm 1<br>2 U2 600V Display                                                                                                                                                        | Idc [A ]                                                                                                      |                                       | 8.688     | -0.003    | 2.642        | 1.     |

| Irms [A                   | ]                |      |                                       | 14.520    | 0.000     | 22.284        | 21.919    | 22.102    | 1.       | 12 200mA                                                                                                                                                                                    | Irms [A ]                                                                                                     |                                       | 10.425    | 0.000     | 10.756       | 10.    |

| P [₩                      | ]                |      |                                       | -13.676k  | 0.000k    | -7.590k       | -7.217k   | -14.807k  |          | LF 100kHz Sync 12<br>FF 0FF Sc Hrm 1                                                                                                                                                        | P [\]                                                                                                         |                                       | 8.689k    | -0.000k   | 2.957k       | 4.     |

| fU [Hz                    | ]                |      |                                       | Error     | 60.001    | 59.998        | 59.962    |           | •        |                                                                                                                                                                                             | fU [Hz]                                                                                                       |                                       | Error     | 60.001    | 60.062       | 59.    |

| Q [var                    | r]               |      |                                       | -4.796k   | 0.000k    | 7.510k        | -7.618k   | -0.108k   | 1   _    | 13 200mA                                                                                                                                                                                    | Q [var]                                                                                                       |                                       | -5.762k   | 0.000k    | -4.227k      | 1.     |

| 72 [%                     | ] E              | rror |                                       |           |           |               |           |           | 9        | LF 100kHz Sync IE<br>FF 0FF Sc Hrm 1 UpdateRate                                                                                                                                             | 72 [%]                                                                                                        | Error                                 |           |           |              |        |

| 73 [%                     | ] E              | rror |                                       |           |           |               |           |           | -        | 4 U4 1000V                                                                                                                                                                                  | 73 [%]                                                                                                        | Error                                 |           |           |              |        |

| T3 P£A 30<br>T6 Udc4 1.   | 0.00kW<br>.500kV |      | · · · · · · · · · · · · · · · · · · · |           |           |               |           | Gr        | oup      | I         14         200mA           LF         100kHz         Sync         IZ           FF         OFF         Sc         Hrm         1           5         U5         600V         Filter | U5 1.800kV<br>15 120.0 A<br>U6 1.800kV<br>16 1220.0 A<br>U7 1.800kV<br>17 120.0 A                             | · · · · · · · · · · · · · · · · · · · |           |           |              |        |

|                           |                  |      |                                       |           |           |               |           |           |          | LF 3kHz Sync IS<br>FF 100Hz SC Hrm 1 Data Save                                                                                                                                              |                                                                                                               | $\mathcal{A}$                         |           |           | $\square$    | $\sum$ |

|                           |                  |      | <u></u>                               |           |           |               |           |           |          | UG 600V<br>16 200mA<br>16 200mA<br>16 200mA<br>11 Integration<br>11 Integration                                                                                                             | 17 -120.0 Å                                                                                                   | $\int$                                | 1         | D         |              |        |

| T6 Udc4 -1.<br>T3 ΡΣΑ -30 | .500k¥           | Ν    | lode -                                | 1: Vdc ı  | egulati   | ion           |           |           |          | U7 600V<br>↓ ↓ 17 200mA<br>↓ LF 3kHz Sync 10 Misc                                                                                                                                           | 17 -1.200 H<br>17 -1.200 K<br>16120.0 A<br>15 -120.0 A<br>15 -120.0 A<br>15 -120.0 A<br>15 -1.800 K<br>0.000s | Μ                                     | ode -2:   | P/Q Co    | ompens       | atic   |

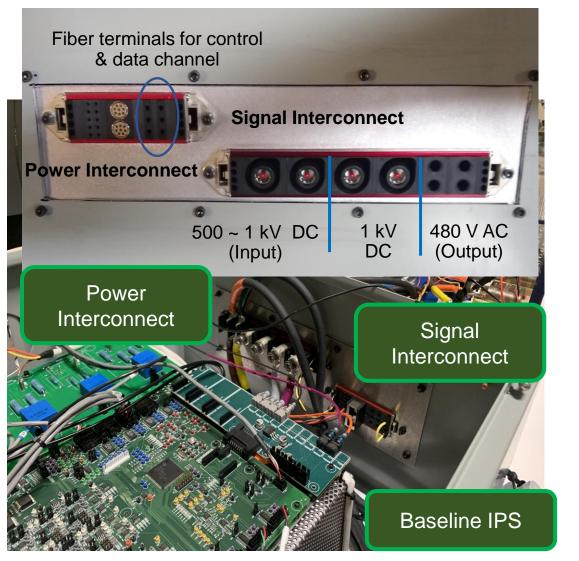

## Innovation Update #3: Standardized Interconnects & Enclosure

- Modular test cell configuration to show interoperability between IPSs from university partners

- Test cell designed to operate at 1kV, 480 V & 150 kVA and be agnostic to IPS design and non-idealities & support parallel operation. Fiber Optic

| 2 | Parameters                      |                 |

|---|---------------------------------|-----------------|

|   | POF Diameter (core)             |                 |

|   | Protective Covering<br>Diameter |                 |

|   | Insertion Loss                  | < 3dB<br>dep    |

|   | Mating cycles                   | Į               |

|   |                                 |                 |

|   | Parameters                      | AC<br>Terminals |

|   | Rated voltage                   | 600 V ac        |

|   | Rated<br>current/contact        | 150 A           |

|   | No. of poles                    | 2               |

|   | Contact diameter                | 8 mm            |

|   | Contact resistance              | < 150 μΩ        |

|   | Mating cycles                   | 100,000         |

|   | Type of termination             | Screw           |

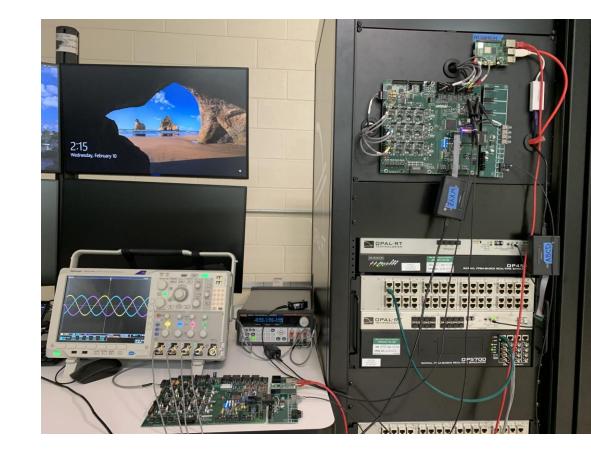

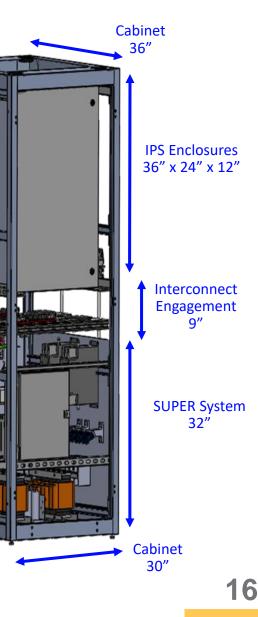

# Innovation Update #4: Standardized SUPER Test Cell

□ Modular test cell configuration to show interoperability between IPSs from university partners

## **Power Routing**

- DC Bus, Intermediate DC Bus, Precharge circuits

- DC Fusing, and DC Main Interconnects

- AC Routing, Filters, to LCL Interface

## **SUPER Auxiliary Supply Routing**

- 480Vac to 24V Supply and Battery backup

- SUPER 15V and 5V Supply

- Wide range DC input to 24V supply

- Interconnect Switch

## LCL Interface

- LCL (configurable for 1 or 2 IPS test positions) and Sensors

- AC Bus, Fusing and Grid Interconnect

## **Shielded Control Cabinet**

- Houses the controller & the communication interfaces

- Receives the signals through the standardized signal interfaces from IPS

## **Engaging & Disengaging Mechanism for the Interconnects**

# Innovation Update #5: IPS Library & Features

## Library of IPSs from university partners to validate **vendor agnostic design** of SUPER

|                                                | Торо                                                         |                                                                         |                                                      |  |

|------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------|--|

| IPS from University Partners                   | DC/DC                                                        | DC/AC                                                                   |                                                      |  |

| Florida state university (FSU)                 | Interleaved buck boost<br>converter with coupled<br>inductor | 3-ph 2-level voltage source inverter (VSI)                              | Interleaved con<br>Input current rip<br>applications |  |

| Ohio State University (OSU)                    | Traditional boost converter                                  | 3-ph 2-level VSI with carrier frequency modulation                      | Capability to int<br>the liquid metal                |  |

| University of Arkansas (UARK)                  | Soft-switching CLLC<br>Bidirectional dc/dc<br>converter      | 3-ph 2-level VSI                                                        | Resonant confi<br>transfer at high<br>soft switching |  |

| University of New York, Stony Brook (NY-SB)    | Interleaved boost converter                                  | 3-ph 2-level VSI with redundant half bridge legs & coupled ac inductors | Capitalizes on I optimize switch                     |  |

| University of North Carolina, Charlotte (UNCC) | -                                                            | 4-leg 3-ph 2-level VSI                                                  | 4-leg configurat                                     |  |

| University of Texas, Austin (UT-Austin)        | DC/DC stage with parallel devices                            | 3-ph 2-level VSI with parallel devices                                  | Parallel devices capability                          |  |

| Virginia Polytechnic University (Vtech)        | 3-level dc/dc converter                                      | 3-ph 2-level VSI                                                        | 3-level configur                                     |  |

\*green color text highlights IPS with discrete devices

## **Features**

onfiguration reduces the ipple. Ideal for BES

ntegrate the inductor with al cooling

figurations for power her frequencies and with

P & N cell layout to hing speeds

ation is suitable for ring applications

es for current handling

uration reduces the EMI

# Innovation Update #5: IPS Library & Features

| IPS Features                                                                                                                                                                                                                                                                                                                                                                                           |   | University Partners                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1. Interoperability <ul> <li>Standardized electrical ports and communication interface</li> <li>Enclosure scalability and standardization</li> <li>Compliance to standards &amp; protocols</li> </ul> </li> </ul>                                                                                                                                                                             | • | Execution by ORNL with al university partners                                                                                                                                                                                                  |

| <ul> <li>2. Embedded intelligence &amp; decision-making capability with a flexible platform</li> <li>Interoperable/scalable with different embedded controllers</li> <li>Monitors the point of connection continuously</li> <li>Easy transition between control mode required by SUPER</li> <li>Immediate response to IPS internal faults with least impact to the SUPER</li> </ul>                    | • | Framework is developed by ORNL and will be c university partners                                                                                                                                                                               |

| <ul> <li>3. Embedded online health monitoring system – Diagnostics/Prognostics</li> <li>Embeds temperature sensors in IPS to enhance thermal monitoring for prognostics</li> <li>Monitors the health and degradation status of critical components in IPS</li> <li>Captures/maps faults to their corresponding signatures</li> <li>Robust/retrievable events recording and reporting system</li> </ul> | • | In-situ on-state resistance measurement (Vtech<br>In-situ junction temperature measurement (UAR<br>In-situ gate leakage current measurement (FSU<br>Estimation of passive components (UARK)<br>DC-link capacitance health estimation (NY-SB, I |

| <ul> <li>4. Integrated minimum passive, intelligent gate driving, sensing and protection</li> <li>Standardized minimum integrated passives</li> <li>Intelligent and robust gate driving scheme</li> <li>Integrated sensing and protective device</li> </ul>                                                                                                                                            | • | Intelligent gate driver (Vtech & FSU)<br>Advanced current sensors (UNCC)<br>Fusion algorithms for sensed signals (OSU)<br>Digital twin for prognostics/diagnostics (NY-SB)                                                                     |

| <ul> <li>5. Cyber-physical security         <ul> <li>Hardware and software mechanisms to secure power electronics systems</li> </ul> </li> </ul>                                                                                                                                                                                                                                                       | - |                                                                                                                                                                                                                                                |

| <ul><li>6. Self-contained auxiliary power supply</li><li>- Draws the required power from IPS itself and power all the contained components</li></ul>                                                                                                                                                                                                                                                   | • | All universities                                                                                                                                                                                                                               |

| S                                             |

|-----------------------------------------------|

|                                               |

|                                               |

|                                               |

| communicated with all                         |

| h, UT-Austin & UNCC)<br>RK & UT-Austin)<br>U) |

| , UNCC, Vtech & UARK)                         |

|                                               |

|                                               |

| 3)                                            |

|                                               |

|                                               |

|                                               |

|                                               |

## **Milestone Update**

| Milestone Description (or Go/No-Go<br>Decision Criteria)                                                                                                                      | Period   | Status    | Accomplishm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1.1 - Validation of SUPER design, operation<br>and controls through simulation and<br>establishing the major IPS design<br>requirements.                                    | BP1 – Q1 | Completed | Identified the hardware, c<br>interface requirements for<br>considering the project of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.2.1 - CHIL validation of the agent<br>framework, the control modes & protection<br>logic and strategy.<br>1.2.2 - 3D layout of the SUPER 1.0 with all its<br>subcomponents. | BP1 – Q2 | Completed | <ul> <li>The entire agent framework protection &amp; communication CHIL.</li> <li>The passives for SUPER validated through simulated through simulated through simulated through simulated through subcomponents has been subcomp</li></ul> |

| 1.3.1 - Preliminary results from open loop testing of SUPER 1.0                                                                                                               | BP1 – Q3 | Completed | <ul> <li>Magnetics prototyping an completed.</li> <li>Standardization details for constraints were articulate partners.</li> <li>Open loop testing of SUP</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>1.4.1 – Experimental results of autonomous operation of SUPER functioning as G with IPS</li> <li>1.0.</li> </ul>                                                     | BP1 – Q4 | Completed | Closed loop operation of validated experimentally validated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## ments/Notes

controls, communications, or SUPER & IPS objectives

vork with the control, ation were validated in

R have been designed and ations. IPER with all its <u>en developed.</u> Ind testing has been

for IPS including ated to the university

PER has been completed.

19

SUPER has been with the agent.

## **Milestone Update**

| Milestone Description (or Go/No-Go<br>Decision Criteria)                                                                                                                                                                                                                                                                                                                    | Due      | Status      | Accomplishm                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|---------------------------------------|

| 2.1.1 - Complete the development of testbed for experimentally validating IPS 2.0 and its subcomponents.                                                                                                                                                                                                                                                                    | BP2 – Q1 | Completed   | The SUPER test cell deve<br>completed |

| 2.2.1 - Complete the performance evaluation<br>and validation of IPS 2.0 power stage from<br>university partners.                                                                                                                                                                                                                                                           | BP2 – Q2 | In Progress |                                       |

| <ul> <li>2.3.1 - Experimental results validating the response of IPS 2.0 for a grid function.</li> <li>2.3.2 – Demonstration of advanced featured of IPS 2.0.</li> </ul>                                                                                                                                                                                                    | BP2 – Q3 | Not Started |                                       |

| <ul> <li>2.4.1 - Demonstration of autonomous</li> <li>operation of SUPER 2.0 functioning as G with</li> <li>IPS 2.0s</li> <li>2.4.2 - Demonstration of SUPER 2.0</li> <li>operating as L</li> <li>2.4.3 - Demonstration of scalability of SUPER</li> <li>2.0 with two non-identical IPS 2.0s</li> <li>Complete the final report with the summary of the results.</li> </ul> | BP2 – Q4 | Not Started |                                       |

## **Risks**

□ Anticipated delays in validation of IPS in the SUPER test cell owing to the pandemic

□ Anticipated delays in the integration of IPS from university partners in the SUPER test cell

## **Future Work**

- □ Validate advanced features like online health monitoring in SUPER with IPSs from partners

- □ Validate advanced algorithms in SUPER for grid support

- Demonstrate the grid support capabilities of SUPER

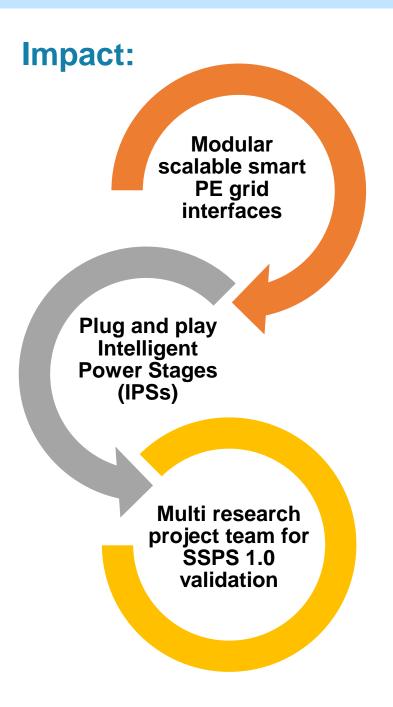

# Impact/Commercialization

- Provides a pathway to develop power electronics interfaces with well defined hierarchy in controls, communication, protection, intelligence and optimization for scalability & modularity

- Provides a pathway to develop a library of power converters for SSPS 1.0

- Provides a pathway for interface, communication, protection standardization

- Provided a pathway to develop holistic systems with embed intelligence & advanced features systematically and strategically in fundamental blocks

- Helps emulate the different vendor scenario to access interoperability & standardization

# Impact/Commercialization

## **Invention Disclosures Filed:**

- □ M. Chinthavali and R. S. K. Moorthy, "Fundamental Building Block Concept and Architecture to Support Solid State Power Substations at the Consumer End".

- □ M. Chinthavali, M. Starke and R. S. K. Moorthy, "Solid State Power Substation (SSPS) Distribution and Consumer End Grid Infrastructure".

## **Publications:**

□ M. Chinthavali, R. S. K. Moorthy and A. Adib, "Standard Modular Architecture for Consumer End Plug and Play Interfaces", in Proc. 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Jun. 2021, Phoenix, AZ, USA.

# **THANK YOU**

# U.S. DEPARTMENT OF OFFICE OF ELECTRICITY