#### Flexible Large Power Solid State Transformer (FLP-SST)

FREEDM Systems Center

North Carolina State University

Dr. Subhashish Bhattacharya

Aug 2019

#### Large power transformer in US electric grid

- ➤ Large power transformers (LPTs) most critical component of the electric grid

- Due to their large physical dimension and custom design are neither interchangeable nor stored as a spare inventory

- ➤ Failure of such LPTs is concern to maintain grid resiliency and reliability since replacement of such LPTs involve longer lead times, special transportation arrangement, man power and capital expenditure.

- To mitigate some of these concern a modular, scalable, efficient and rapid recovery solution is proposed.

Transportation of a large power transformer.

#### **Project Objectives**

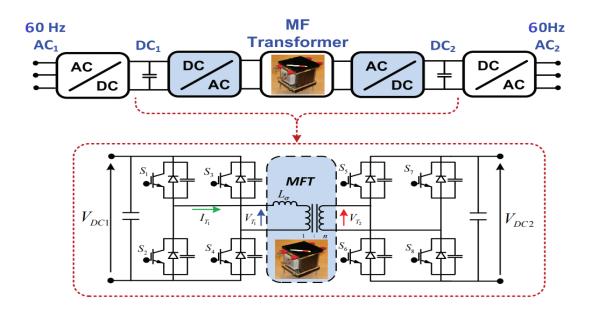

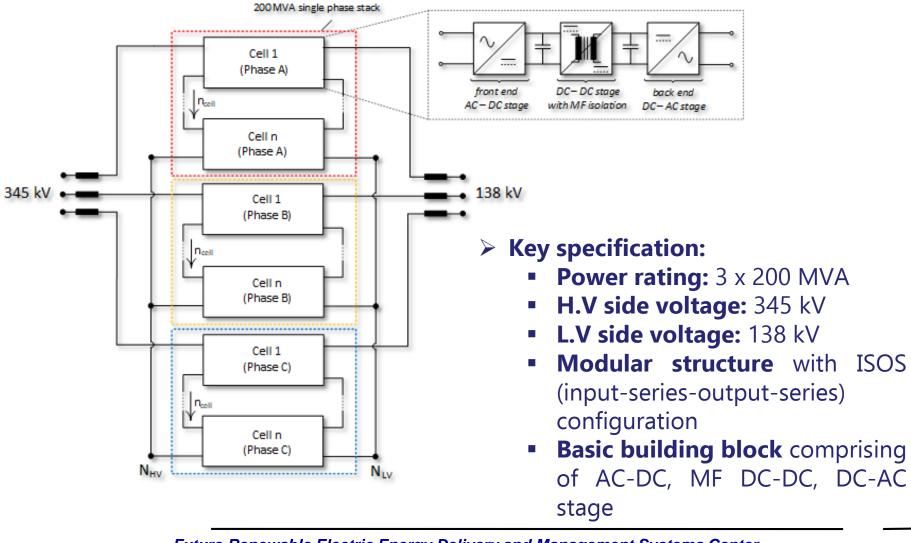

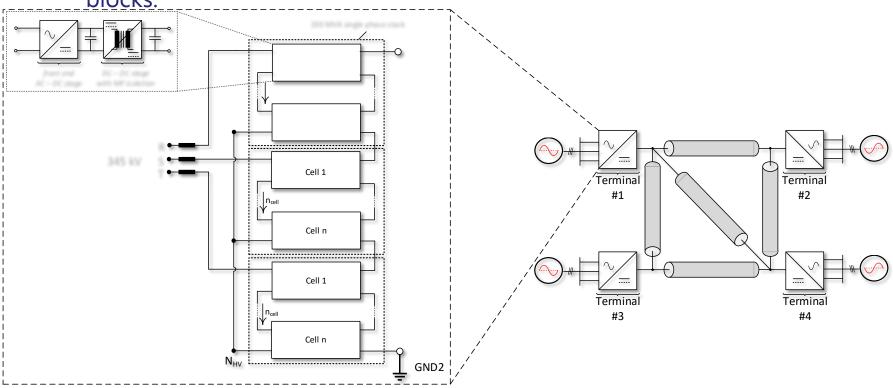

A modular solution, where flexible voltage ratings will be achieved by series/parallel connection of a basic building block (a power electronics based medium frequency transformer to achieve required voltage isolation and variable step-up and step-down voltage ratios)

#### **Technical Approach**

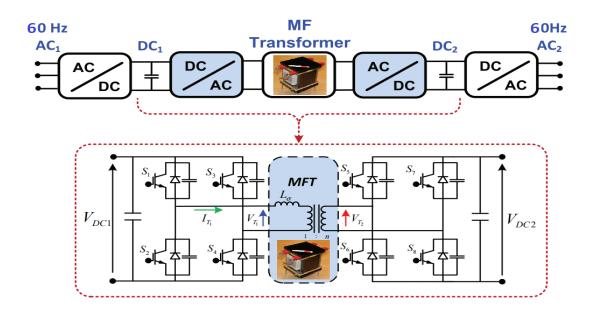

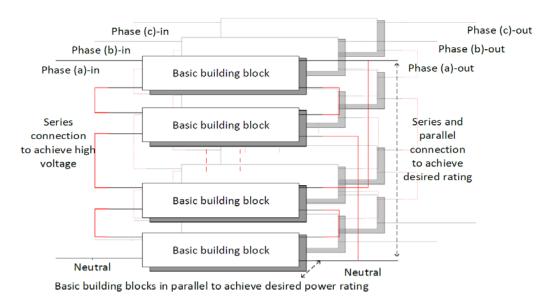

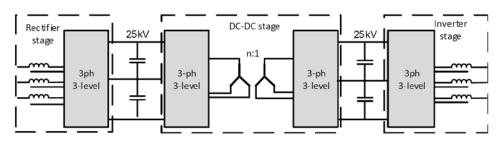

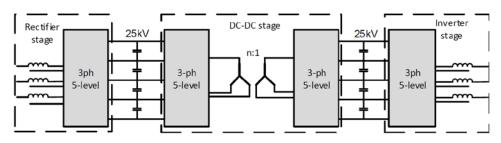

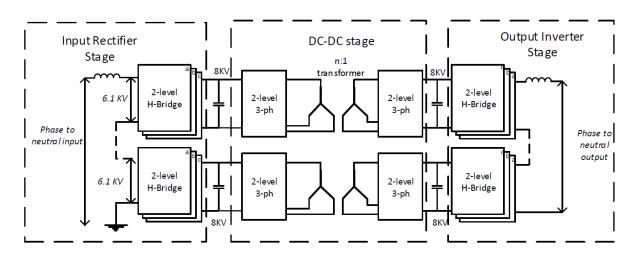

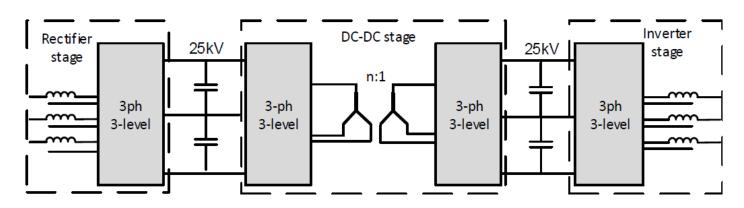

- A basic building block of consisting of the following stages to form Flexible Large Power Solid State Transformers.

- AC-DC Rectifier Stage

- 2. Isolated DC-DC transformer converter stage, with medium-frequency transformer with variable buck-boost voltage step-up and step down ratios.

- 3. DC-AC inverter stage

#### **Technical Approach**

FLPSST realization using series and parallel connection of the basic building blocks.

10kV and 15kV MOSFETs/IGBTs open up possibility of using simple circuitry. Also they reduce size and enable air cooled thermal management.

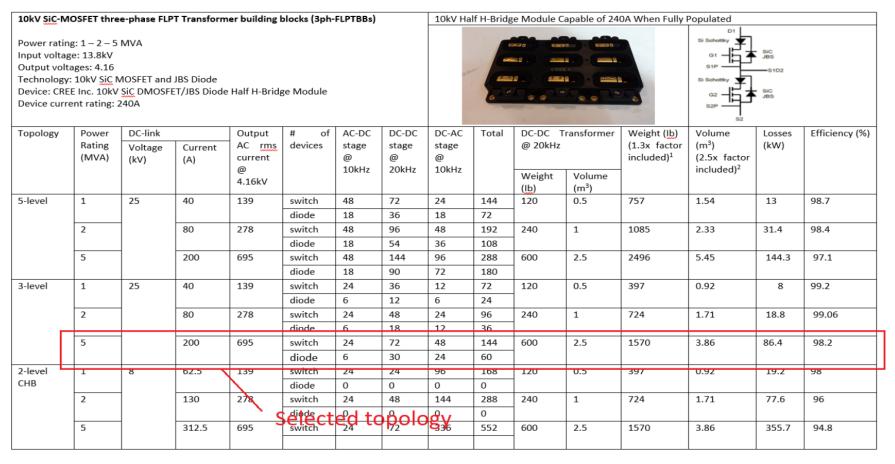

preliminary assessment of 1, 2 and 5 MVA basic building blocks were carried out using the latest medium voltage SiC devices.

- 1. 10 kV SiC-MOSFET and 15 kV JBS Diode.

- 15 kV SiC-IGBT and 15 kV JBS Diode.

3-level FLPT-BB topology using 10kV SiC-MOSFET devices.

5-level FLPT-BB topology using 10kV SiC-MOSFET devices.

preliminary assessment of 1, 2 and 5 MVA basic building blocks were carried out using the latest medium voltage SiC devices.

- 1. 10 kV SiC-MOSFET and 15 kV JBS Diode.

- 2. 15 kV SiC-IGBT and 15 kV JBS Diode.

2-level Cascade H-Bridge (2L-CHB) FLPT-BB using 10kV SiC-MOSFETs.

preliminary assessment of 1, 2 and 5 MVA basic building blocks were carried out using the latest medium voltage SiC devices.

- 10 kV SiC-MOSFET and 15 kV JBS Diode.

- 2. 15 kV SiC-IGBT and 15 kV JBS Diode.

3-level FLPT-BB topology using 15kV SiC-MOSFET devices.

#### **Summary**

- 1. 10 kV SiC-MOSFET and 15 kV JBS Diode.

- 15 kV SiC-IGBT and 15 kV JBS Diode.

10kV SiC-IGBT/JBS Diode three-phase FLPSST possible building blocks.

### Flexible Large Power Solid State Transformer (FLPSST)

#### > System overview and key specifications

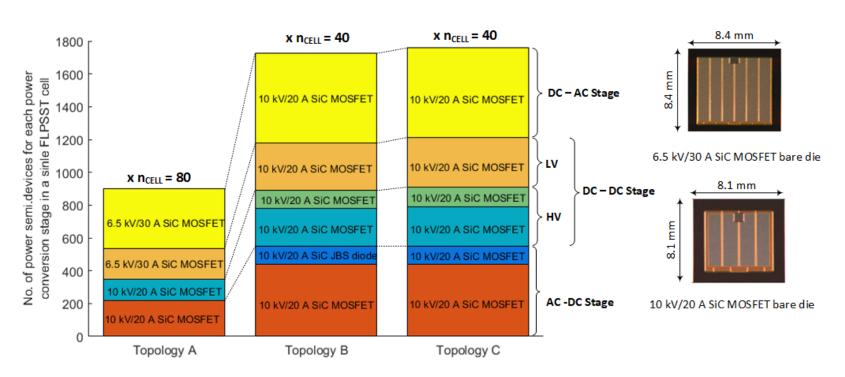

#### Power semiconductor devices

- > 6.5 kV SiC MOSFET

- **V**<sub>DS</sub>: 6.5 kV

- **I**<sub>D</sub>: 30 A

- specific  $R_{DS(on)}$ : 80 m $\Omega$

8.4 mm x 8.4 mm 6.5 kV SiC MOSFET bare die

- > 10 kV SiC MOSFET

- **V**<sub>DS</sub>: 10 kV

- **I**<sub>D</sub>: 20 A

- Specific  $R_{DS(on)}$ : 350 m $\Omega$

8.1 mm x 8.1 mm 10 kV SiC MOSFET bare die

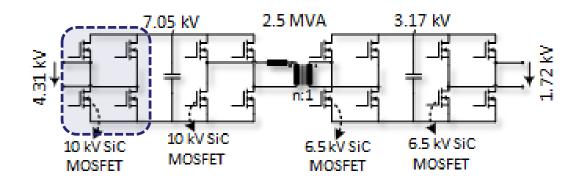

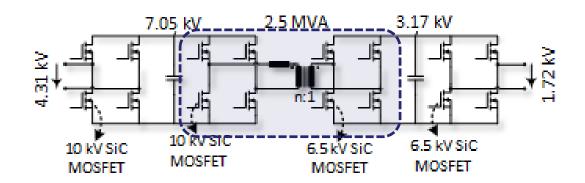

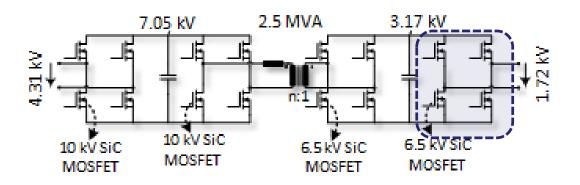

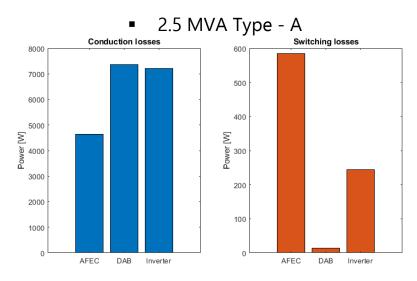

#### 2.5 MVA basic building block topology: Type - A

- **Power rating:** 2.5 MVA

- **n**<sub>cell</sub>: 80

| Parameter                                                         | Value                                            |

|-------------------------------------------------------------------|--------------------------------------------------|

| Cell input side DC link voltage                                   | 7.05 kV                                          |

| Cell input side AC rms voltage and current                        | 4.31 kV, 579.12 A                                |

| Cell input side peak current                                      | 818.99 A                                         |

| Cell AC-DC stage switching frequency                              | 10 kHz                                           |

| Cell AC-DC stage devices<br>Number of devices per switch position | 10 kV SiC MOSFETs<br>55 x 10 kV/20 A SiC MOSFETs |

#### 2.5 MVA basic building block topology: Type - A

- Power rating: 2.5

- MVA n<sub>cell</sub>: 80

| Parameter                                                                        | Value                                                  |

|----------------------------------------------------------------------------------|--------------------------------------------------------|

| Cell DC-DC stage transformer specification                                       | n:1 = 2.22, L <sub>lkg</sub> ≈ 183 µH, VA = 2.5<br>MVA |

| Cell AC-DC stage switching frequency                                             | 10 kHz                                                 |

| Cell DC-DC stage primary side devices<br>Number of devices per switch position   | 10 kV SiC MOSFETs<br>55 x 10 kV/20 A SiC MOSFETs       |

| Cell DC-DC stage secondary side devices<br>Number of devices per switch position | 6.5 kV SiC MOSFETs<br>55 x 6.5 kV/30 A SiC MOSFETs     |

#### 2.5 MVA basic building block topology: Type - A

Power rating: 2.5 MVA

• **n**<sub>cell</sub>: 80

| Parameter                                                         | Value                                             |

|-------------------------------------------------------------------|---------------------------------------------------|

| Cell input side DC link voltage                                   | 3.17 kV                                           |

| Cell input side AC rms voltage and current                        | 1.72 kV, 1449.27 A                                |

| Cell input side peak current                                      | 2049.58 A                                         |

| Cell DC-AC stage switching frequency                              | 10 kHz                                            |

| Cell DC-AC stage devices<br>Number of devices per switch position | 6.5 kV SiC MOSFETs<br>91 x 10 kV/20 A SiC MOSFETs |

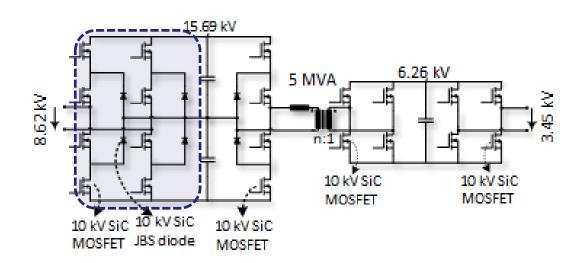

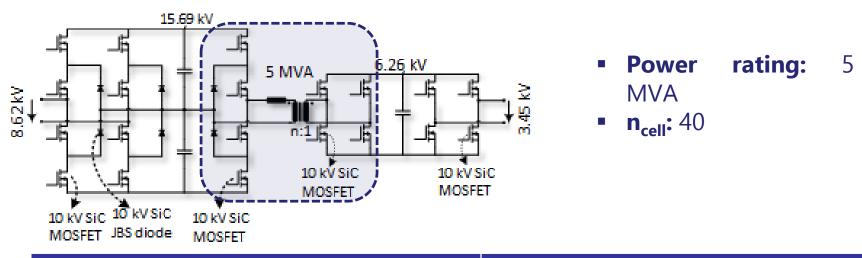

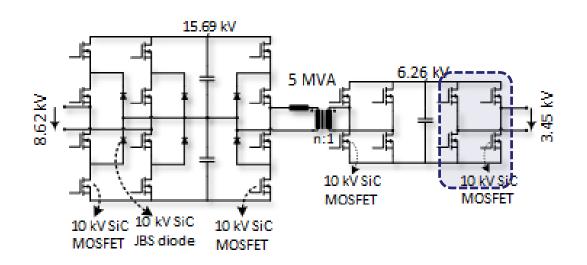

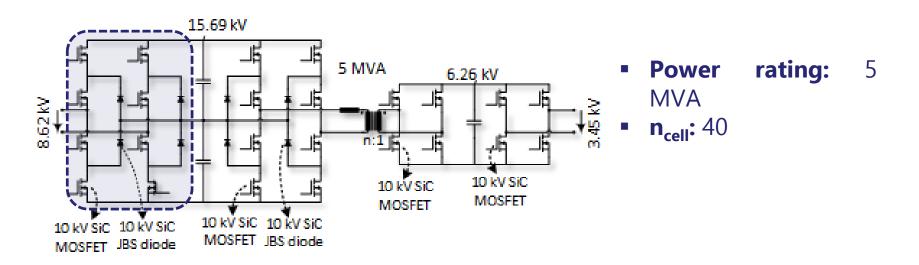

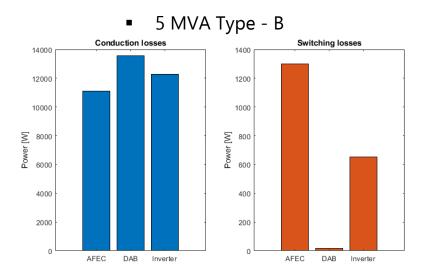

## FREE 5 MVA basic building block topology: Type - B

- **Power rating:** 5 MVA

- **n**<sub>cell</sub>: 40

| Parameter                                                       | Value                                                                       |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------|

| Cell input side DC link voltage                                 | 15.69 kV                                                                    |

| Cell input side AC rms voltage and current                      | 8.62 kV, 579.12 A                                                           |

| Cell input side peak current                                    | 818.99 A                                                                    |

| Cell AC-DC stage switching frequency                            | 10 kHz                                                                      |

| Cell AC-DC stage devices  Number of devices per switch position | 10 kV SiC MOSFETs & JBS diode<br>55 x 10 kV/20 A SiC MOSFETs & JBS<br>diode |

## 5 MVA basic building block topology: Type - B

| Parameter                                                                        | Value                                                         |

|----------------------------------------------------------------------------------|---------------------------------------------------------------|

| Cell DC-DC stage transformer specification                                       | n:1 = 1.25, L <sub>lkg</sub> ≈ 115 μH, VA = 5 MVA             |

| Cell AC-DC stage switching frequency                                             | 10 kHz                                                        |

| Cell DC-DC stage primary side devices<br>Number of devices per switch position   | 10 kV SiC MOSFETs & JBS diodes<br>57 x 10 kV/20 A SiC MOSFETs |

| Cell DC-DC stage secondary side devices<br>Number of devices per switch position | 10 kV SiC MOSFETs<br>71 x 10 kV/20 A SiC MOSFETs              |

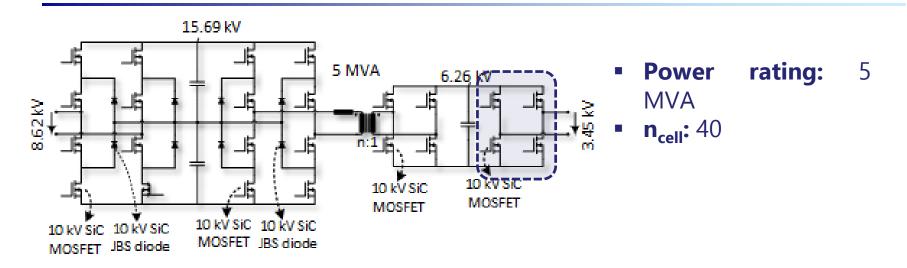

## FREE 5 MVA basic building block topology: Type - B

- **Power rating:** 5 MVA

- **n**<sub>cell</sub>: 40

| Parameter                                                         | Value                                             |

|-------------------------------------------------------------------|---------------------------------------------------|

| Cell input side DC link voltage                                   | 6.26 kV                                           |

| Cell input side AC rms voltage and current                        | 3.45 kV, 1449.27 A                                |

| Cell input side peak current                                      | 2049.58 A                                         |

| Cell DC-AC stage switching frequency                              | 10 kHz                                            |

| Cell DC-AC stage devices<br>Number of devices per switch position | 10 kV SiC MOSFETs<br>137 x 10 kV/20 A SiC MOSFETs |

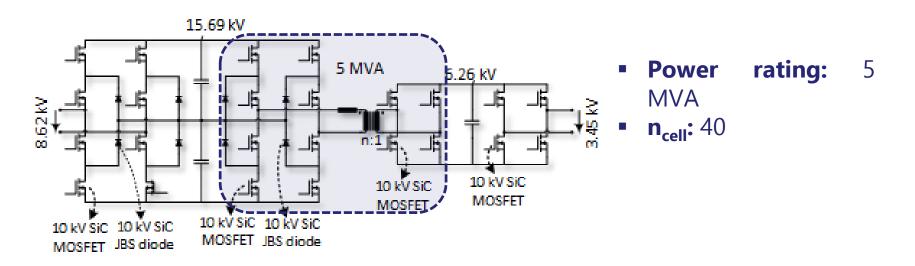

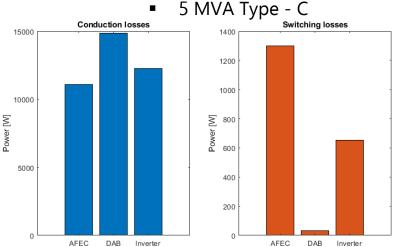

#### 5 MVA Basic building block topology: Type - C

| Parameter                                                         | Value                                                                       |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Cell input side DC link voltage                                   | 15.69 kV                                                                    |

| Cell input side AC rms voltage and current                        | 8.62 kV, 579.12 A                                                           |

| Cell input side peak current                                      | 818.99 A                                                                    |

| Cell AC-DC stage switching frequency                              | 10 kHz                                                                      |

| Cell AC-DC stage devices<br>Number of devices per switch position | 10 kV SiC MOSFETs & JBS diode<br>55 x 10 kV/20 A SiC MOSFETs & JBS<br>diode |

#### 5 MVA basic building block topology: Type - C

| Parameter                                                                        | Value                                                      |

|----------------------------------------------------------------------------------|------------------------------------------------------------|

| Cell DC-DC stage transformer specification                                       | n:1 = 2.5, , L <sub>lkg</sub> ≈ 437 μH, VA = 5<br>MVA      |

| Cell AC-DC stage switching frequency                                             | 10 kHz                                                     |

| Cell DC-DC stage primary side devices<br>Number of devices per switch position   | 10 kV SiC MOSFETs & JBS diodes 30 x 10 kV/20 A SiC MOSFETs |

| Cell DC-DC stage secondary side devices<br>Number of devices per switch position | 10 kV SiC MOSFETs<br>75 x 10 kV/20 A SiC MOSFETs           |

#### 5 MVA basic building block topology: Type - C

| Parameter                                                       | Value                                             |

|-----------------------------------------------------------------|---------------------------------------------------|

| Cell input side DC link voltage                                 | 6.26 kV                                           |

| Cell input side AC rms voltage and current                      | 3.45 kV, 1449.27 A                                |

| Cell input side peak current                                    | 2049.58 A                                         |

| Cell DC-AC stage switching frequency                            | 10 kHz                                            |

| Cell DC-AC stage devices  Number of devices per switch position | 10 kV SiC MOSFETs<br>137 x 10 kV/20 A SiC MOSFETs |

# Comparison of basic building block topologies in terms of power semiconductor device requirements

Amongst three topologies Type – B configuration utilizes lowest number of power semiconductor devices and number of series connected modules per phase stack.

### Comparison of basic building block topologies in terms of power semiconductor losses

Power semiconductor losses expressed as a percentage of rated power.

| FLPSST<br>building block | Semiconductor losses (% of rated power) |

|--------------------------|-----------------------------------------|

| Type - A                 | ≈ 0.8 %                                 |

| Type – B                 | ≈ 0.77 %                                |

| Type – C                 | ≈ 0.8 %                                 |

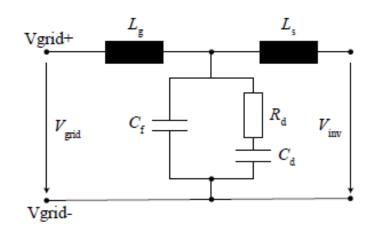

#### 13.8 KV Grid Side Converter Design LCL Filter

#### ► Filter specifications

- Total impedance is 0.1 p.u.  $(X_{L_c} + X_{L_i} = 0.1 \text{ p.u.})$

- $\bullet$  Maximum reactive power of filter capacitor ( $C_{\scriptscriptstyle f}$  ) is 10%

- Resonance frequency  $(f_{res})$ :  $7f_{grid} < f_{res} < \frac{1}{5}f_{sw}$

- Q is choosen to be 3 and the damping resistor is designed.

Based on the specifications, the calculated parameters for 13.8 KV LCL filter is summarized as follow,

| Parameters                                      | Designed Value |

|-------------------------------------------------|----------------|

| Converter side Inductance ( $L_s$ )             | 8.8 mH         |

| Grid side Inductance ( $L_g$ )                  | 1.3 mH         |

| Capacitances (C <sub>f</sub> , C <sub>d</sub> ) | 7 μF           |

| Damping Resistance ( $R_d$ )                    | 4.17 Ω         |

### MV MF isolation transformer for FLPSST basic building blocks

#### **Key challenges:**

- High isolation voltage requirements

- Isolation coordination set by top most cell in a phase stack.

- Mixed frequency medium voltage electric field stresses

- Low isolation capacitance requirements

- Thermal management

- Magnetic core material

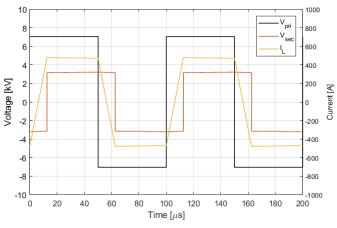

MV MF isolation transformer primary, secondary winding voltages and currents for basic building block topologies.

2.5 MVA Type - A

**Power rating: 2.5 MVA**

Max. diff. voltage stress: 7.05 kV

Max. rms and peak winding

**currents:** ≈ 1040 A, 944 A

(Two level voltage waveform)

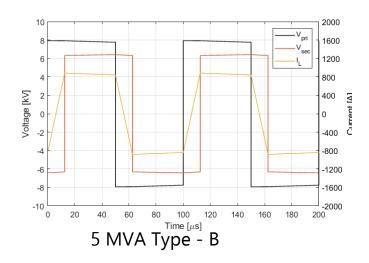

**Power rating:** 5 MVA

**Max. diff. voltage stress:** ≈ 7.89 kV

Max. rms and peak winding currents:

≈ 1105 A, 986 A

(Two level voltage waveform)

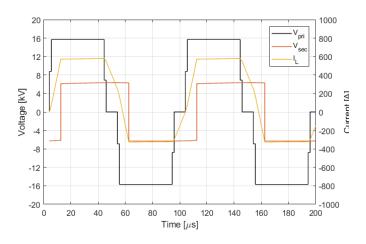

5 MVA Type - C

**Power rating:** 5 MVA

Max. diff. voltage stress: ≈ 15.69 kV

Max. rms and peak winding currents: ≈

1445 A, 1041 A

(Two level voltage waveform)

#### > MV MF isolation transformer for FLPSST basic building blocks

#### **Key challenges:**

- High isolation voltage requirements

- Isolation coordination set by top most cell in a phase stack.

- Mixed frequency medium voltage electric field stresses

- Low isolation capacitance requirements

- Thermal management

- Magnetic core material

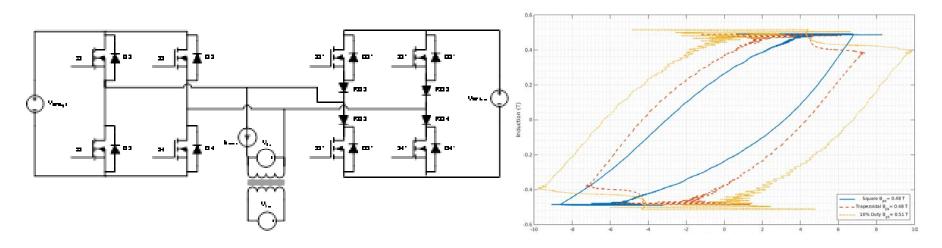

Test set up for characterizing the magnetic core materials under trapezoidal excitation.

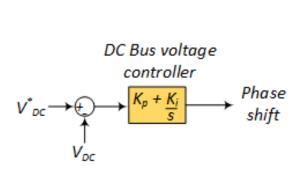

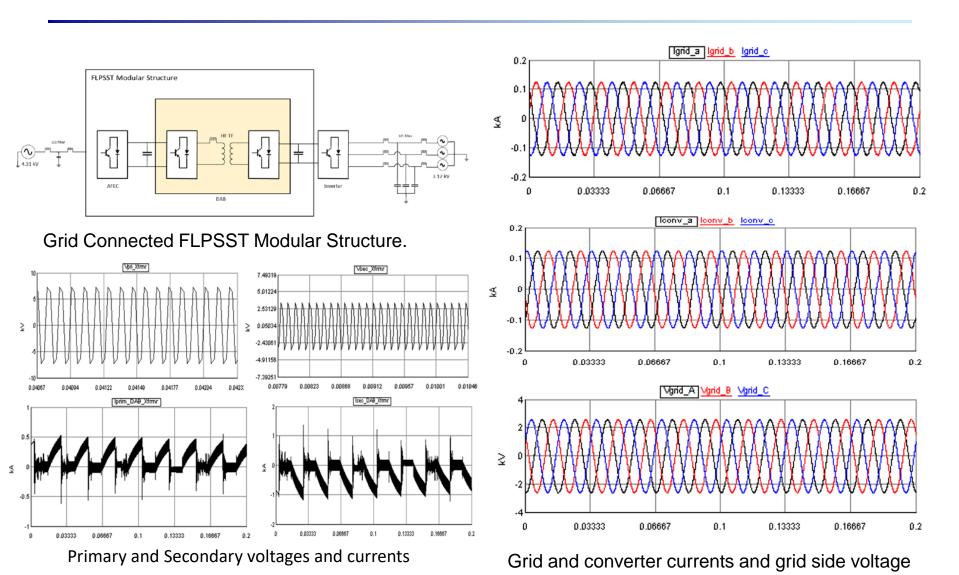

- DC bus voltage controller

- Notch filter for 120 Hz voltage ripple filtering (inherent power pulsation at twice the grid frequency in single phase system)

- Active and reactive power control with synchronous reference frame dq current control

- Controller bandwidth and tuning is performed following method presented in

- DC bus voltage controller

- Notch filter for 120 Hz voltage ripple filtering (inherent power pulsation at twice the grid frequency in single phase system)

- Active and reactive power control with synchronous reference frame dq current control

- Controller bandwidth and tuning is performed following method presented in <a>28</a>

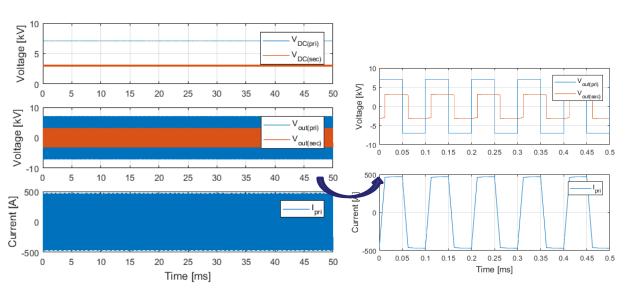

Schematic of an DAB control loop implementation

Simulation results for 2.5 MVA DAB (Type - C)

- DC bus voltage controller controls the DC bus voltage at the secondary side of the DAB.

- Loading of the LV side inverter generates power pulsation at twice the grid fundamental frequency,

- The DAB LV capacitance size requirement is relatively higher to maintain the voltage ripple within the acceptable limit and for proper functioning of the PPI controller.

Future Renewable Electric Energy Delivery and Management Systems Center

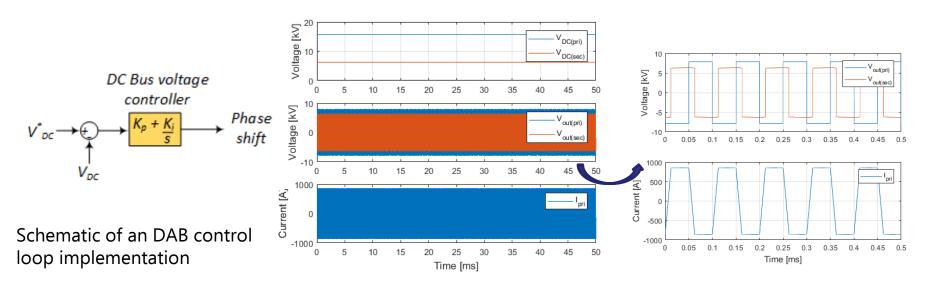

Simulation results for 5MVA DAB (Type B)

- DC bus voltage controller controls the DC bus voltage at the secondary side of the DAB.

- Loading of the LV side inverter generates power pulsation at twice the grid fundamental frequency,

- The DAB LV capacitance size requirement is relatively higher to maintain the voltage ripple within the acceptable limit and for proper functioning of the PI controller.

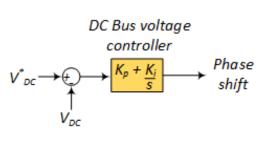

Schematic of an DAB control loop implementation

Simulation results for 5 MVA DAB

- DC bus voltage controller controls the DC bus voltage at the secondary side of the DAB.

- Loading of the LV side inverter generates power pulsation at twice the grid fundamental frequency,

- The DAB LV capacitance size requirement is relatively higher to maintain the voltage ripple within the acceptable limit and for proper functioning of the PI controller.

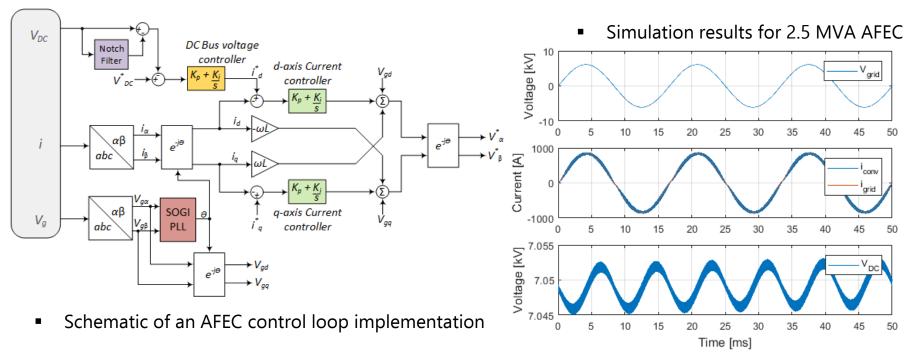

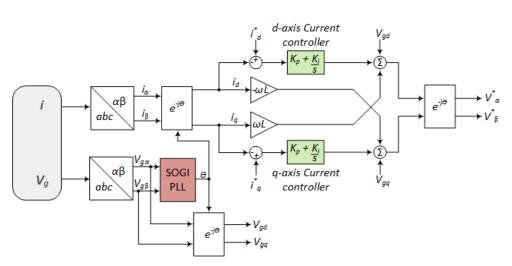

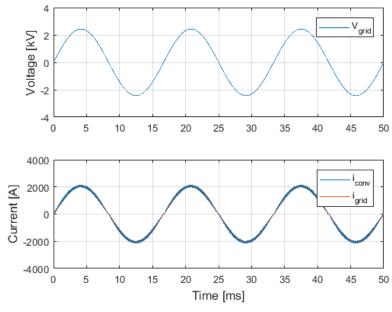

Schematic of an inverter control loop implementation

Simulation results for 2.5 MVA Inverter

- Active and reactive power control with synchronous reference frame dq current control

- Controller bandwidth and tuning is performed following method presented in [].

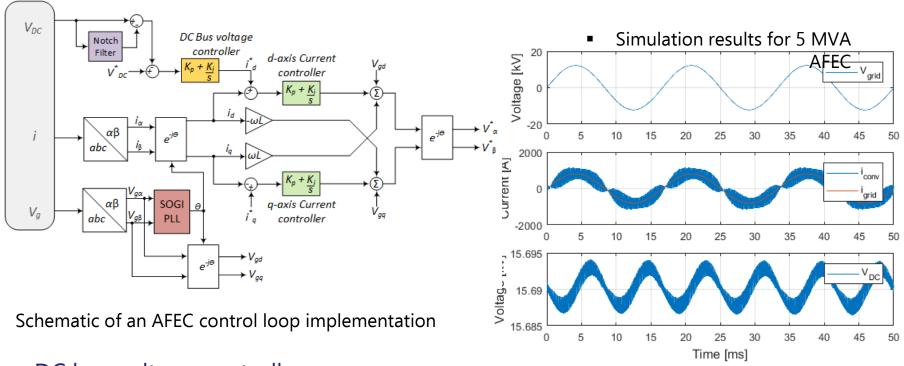

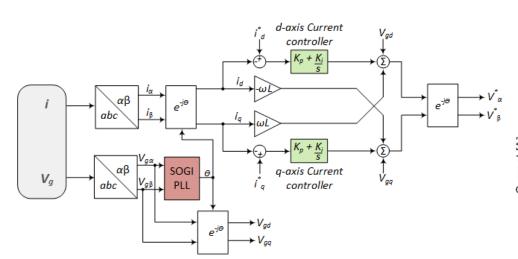

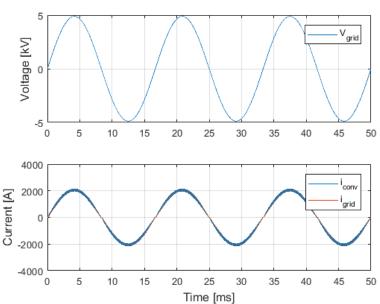

Schematic of an inverter control loop implementation

Simulation results for 5 MVA Inverter

- Active and reactive power control with synchronous reference frame dq current control

- Controller bandwidth and tuning is performed following method presented in [].

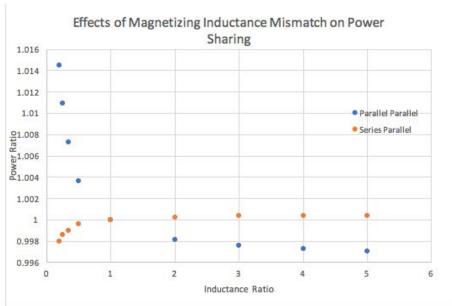

#### **Power Sharing in Low Frequency Transformers**

#### Goal

To assess the feasibility of modular low frequency transformers and investigate impact of transformer parameter mismatch on current and voltage sharing in low-frequency, modular, large-power-transformers

#### **Problem**

- **Current sharing** important to prevent transformers from caring too much current causing them to overheat and degrade

- Voltage sharing important to prevent transformers from exceeding rated insulation. Also important to avoid magnetic core saturation, which causes output voltage distortion and high magnetizing current

#### **Power Sharing in Low Frequency Transformers**

#### **Example transformer specs:**

#### **Example transformer specs:**

5 MVA, 100 kV:10 kV

Leakage inductance: 10% (5% primary, 5% secondary)

Magnetizing current: 1%

Load: 5 MVA, PF 0.5

Transformer losses: none

Calculated:

| Primary                                      | Secondary                               |

|----------------------------------------------|-----------------------------------------|

| Z <sub>base</sub> : 2 kOhm                   | Z <sub>base</sub> : 20 Ohm              |

| L <sub>leakage</sub> : j100 Ohm = 265 mH     | L <sub>leakage</sub> : j1 Ohm = 2.65 mH |

| I <sub>base</sub> : 50 A                     |                                         |

| I <sub>magnetizing</sub> : 500 mA            |                                         |

| L <sub>magnetizing</sub> : j200 kOhm = 530 H |                                         |

#### **Power Sharing in Low Frequency Transformers**

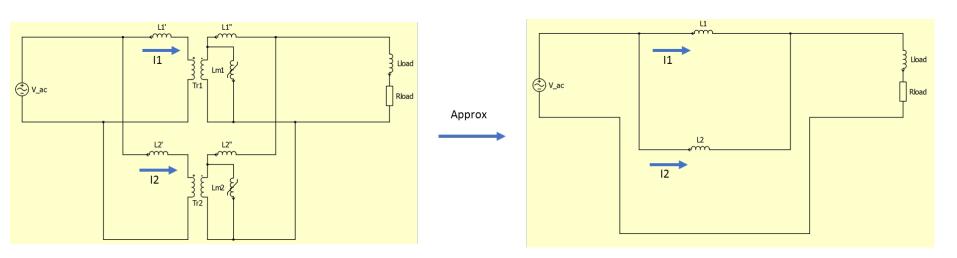

#### **Parallel-Parallel Connection**

- Parallel transformers provide redundancy and increase the power capacity

- The two transformers must have the same voltage ratings and turns ratios to avoid circulating current.

$$I_1 \cong I_{total} rac{L_{l2}}{L_{l1} + L_{l2}}$$

(if magnetizing inductance is ignored)

Future Renewable Electric Energy Delivery and Management Systems Center

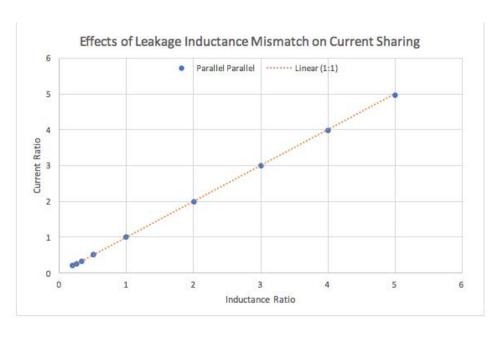

#### **Parallel-Parallel Connection**

Effect of leakage and magnetizing inductances mismatches on the current sharing

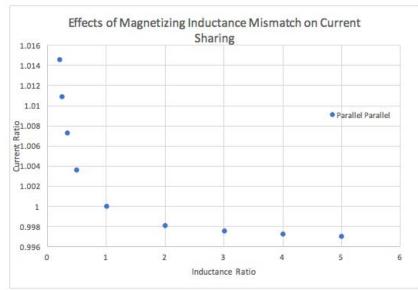

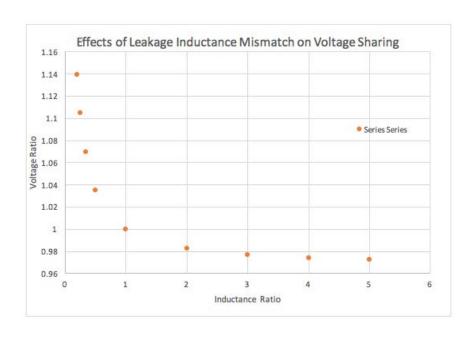

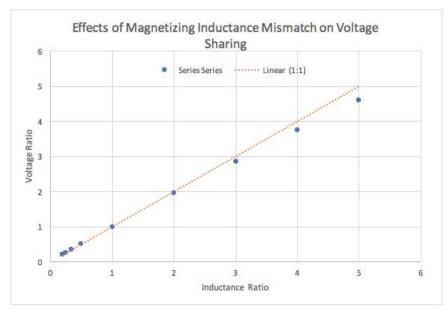

#### **Series-Series Connection**

$$V_1 \cong V_{total} rac{L_{m1}}{L_{m1} + L_{m2}}$$

(leakage inductance << magnetizing inductance)

#### **Series-Series Connection**

Effect of leakage and magnetizing inductances mismatches on the current sharing

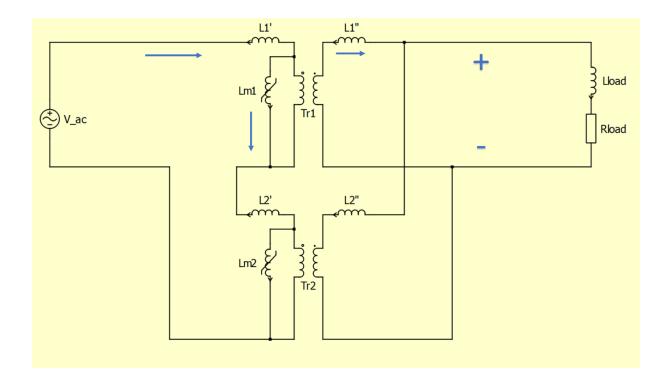

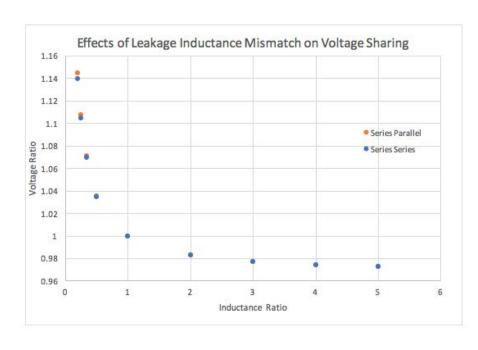

## **Series-Parallel Connection**

#### **Series-Parallel Connection**

Effect of leakage and magnetizing inductances mismatches on the current sharing

## **Summary**

The following table summarizes the level of sensitivity of each type of mismatch on the voltage and current sharing of the different types of transformer connections.

|                       |                    | Leakage Inductance<br>Mismatch | Largest<br>Ratio  | Magnetizing Inductance<br>Mismatch | Largest<br>Ratio |

|-----------------------|--------------------|--------------------------------|-------------------|------------------------------------|------------------|

| Parallel-<br>Parallel | Voltage<br>Sharing | Perfect Sharing                | 1                 | Perfect Sharing                    | 1                |

|                       | Current<br>Sharing | Near Proportional              | 4.95              | Near Perfect Sharing               | 1.01             |

| Series-<br>Series     | Voltage<br>Sharing | Good Sharing                   | <mark>1.14</mark> | Near Proportional                  | 4.6              |

|                       | Current<br>Sharing | Perfect Sharing                | 1                 | Perfect Sharing                    | 1                |

| Series-<br>Parallel   | Voltage<br>Sharing | Good Sharing                   | 1.14              | Very Near Perfect Sharing          | 1.002            |

|                       | Current<br>Sharing | Perfect Sharing                | 1                 | Perfect Sharing                    | 1                |

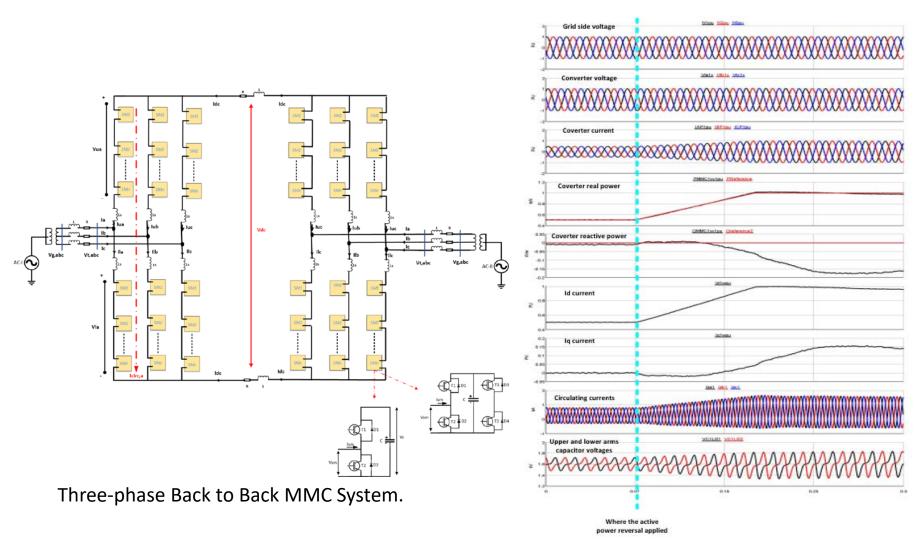

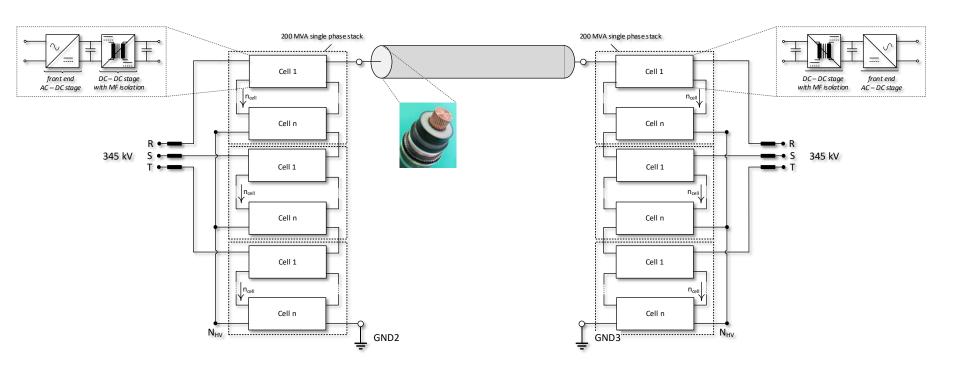

# Modular Multi-cell FLPSST based on single phase building blocks

MMC Output Waveform.

## Real-Time Simulation of Single Phase AC to Three Phase SST

Future Renewable Electric Energy Delivery and Management Systems Center

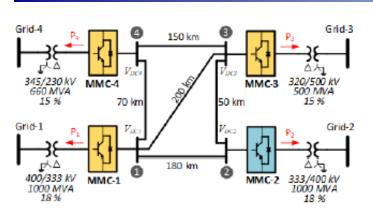

## > Possible applications: Back to back two terminal DC system

The FLPSST basic building blocks can be utilized to form the two terminal isolated high voltage DC network.

## Possible applications: Back to back two terminal DC system

A muli-terminal HVDC system realization using the FLPSST basic building blocks.

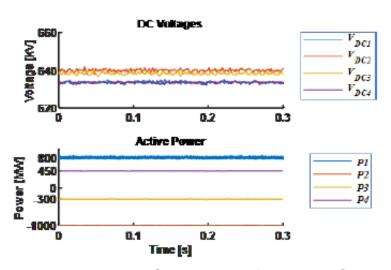

## Performance Evaluation of Four-Terminal MTDC System

Four-Terminal MMC based-MTDC configuration

RTDS and MMC support unit hardware

Droop control characteristics of MMCs

Active powers and DC voltages of the MTDC system under steady-state conditions

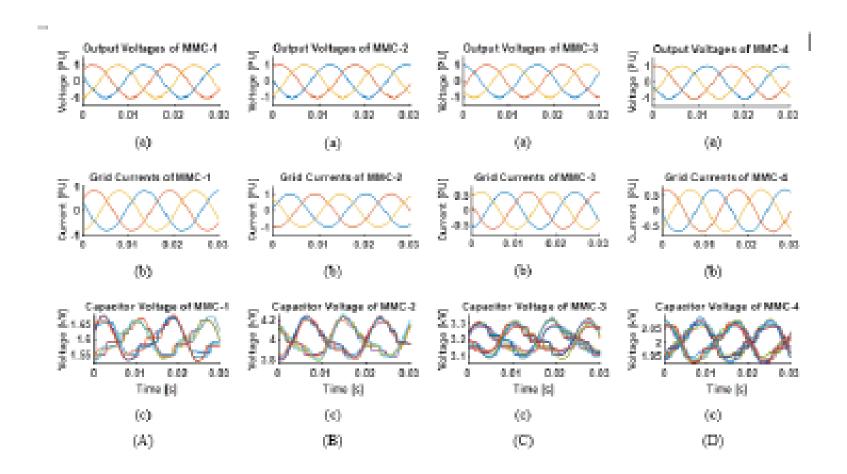

RTDS results at the steady states, (a) AC output voltages, (b) grid currents, and (c) upper and lower arm SM capacitor voltages: (A) MMC-1, (B) MMC-2, (C) MMC-3, (D) MMC-4

#### References

- [1] CONSIDERATIONS FOR A POWER TRANSFORMER EMERGENCY SPARE STRATEGY FOR THE ELECTRIC UTILITY INDUSTRY, The Electric Power Research Institute for the U.S. Department of Homeland Security Science and Technology Directorate, September, 2014.

- [2] LARGE POWER TRANSFORMERS AND THE U.S.ELECTRIC GRID, Infrastructure Security and Energy Restoration Office of Electricity Delivery and Energy Reliability U.S. Department of Energy, June 2012.

- [3] Jaffery B. Casady et al., "Medium voltage SiC R & D update, "https://www.nist.gov/sites/default/files/documents/pml/high\_megawatt/Wolfspeed-Cree-SiC-Pwr-NIST-wkshp-Apr2016\_SHORT.pdf

- [4] S. Sabri et al., "New generation 6.5 kV SiC power MOSFET," 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, 2017, pp. 246-250. doi: 10.1109/WiPDA.2017.8170555

- [5] D. Johannesson, M. Nawaz and K. Ilves, "Assessment of 10 kV, 100 A Silicon Carbide mosfet Power Modules," in IEEE Transactions on Power Electronics, vol. 33, no. 6, pp. 5215-5225, June 2018.

- [6] S. Ji, S. Zheng, Z. Zhang, F. Wang, and L. M. Tolbert. Protection and temperature-dependent switching characterization of latest generation 10 kv sic mosfets. In2017IEEE Applied Power Electronics Conference and Exposition (APEC), pages 783–788, March 2017. doi: 10.1109/APEC.2017.7930784

- [7] D. Rothmund, D. Bortis and J. W. Kolar, "Accurate transient calorimetric measurement of soft-switching losses of 10kV SiC MOSFETs," 2016 IEEE 7th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Vancouver, BC, 2016, pp. 1-10.