## FY 2016 Annual Progress Report for Electric Drive Technologies Program

July 2017

## **CONTENTS**

| ACI | RONY  | MS AND ABBREVIATIONS                                                                       | xvi |

|-----|-------|--------------------------------------------------------------------------------------------|-----|

| INT | RODI  | UCTION                                                                                     | 20  |

|     | 1.1   | Electric Drive Technologies Research and Development                                       | 20  |

|     | 1.2   | FY 2016 Accomplishments                                                                    | 22  |

|     |       | 1.2.1 High Power Density Ferrite PM Motor                                                  |     |

|     |       | 1.2.2 Using Supercomputers to Develop Better Magnetic Materials                            | 23  |

|     |       | 1.2.3 Materials Expertise Aids Manufacturers in Manufacturing and Commercialization of     |     |

|     |       | High-Performance Motors                                                                    |     |

|     |       | 1.2.4 High Temperature DC Bus Capacitor Cost Reduction & Performance Improvements          | 25  |

|     |       | 1.2.5 Vehicle Electric Motor Design Uses Permanent Magnets Without Any Rare Earth  Content | 26  |

|     |       | 1.2.6 Application of SiC Power Devices in Hybrid Electric Vehicle Drive Systems            |     |

|     |       | 1.2.7 High Temperature, Wide Bandgap (WBG) Inverter for Electric Vehicles                  |     |

|     |       | 1.2.8 Thermal Management of WBG Technology Critical for Power-Dense and High-              |     |

|     |       | Temperature Systems                                                                        | 29  |

|     | 1.3   | Small Business Innovative Research Grants                                                  |     |

| DEC |       | CH AREAS                                                                                   |     |

|     |       |                                                                                            |     |

| 2   |       | tric Motor Research and Development                                                        |     |

|     | 2.1   | Advanced Electric Motor Research                                                           |     |

|     | 2.2   | Electric Motor Performance Improvements Techniques                                         |     |

|     | 2.3   | Electric Motor Thermal Management Research                                                 |     |

|     | 2.4   | Brushless and Permanent Magnet Free Wound Field Synchronous Motors for EV Traction         |     |

|     | 2.5   | Alternative High-Performance Motors with Non-Rare Earth Materials                          | 85  |

|     | 2.6   | Unique Lanthanide-Free Motor Construction                                                  | 94  |

| 3   | Powe  | er Electronics Research and Development                                                    | 110 |

|     | 3.1   | Electric Drive Wide Bandgap Power Electronics                                              | 110 |

|     | 3.2   | Wide Bandgap Converters and Chargers                                                       | 124 |

|     | 3.3   | Gate Driver Optimization for WBG Applications                                              | 137 |

|     | 3.4   | Power Electronics Thermal Management Research                                              | 146 |

|     | 3.5   | Highly Integrated Wide Bandgap Power Module for Next Generation Plug-In Vehicles           | 159 |

|     | 3.6   | 88 Kilowatt Automotive Inverter with New 900 Volt Silicon Carbide MOSFET Technology        | 167 |

|     | 3.7   | A Disruptive Approach to Electric Vehicle Power Electronics                                | 181 |

| 4   | Benc  | chmarking, Testing, and Analysis                                                           | 196 |

|     | 4.1   | Benchmarking Electric Vehicles and Hybrid Electric Vehicles                                | 196 |

|     | 4.2   | Thermal Performance Benchmarking                                                           |     |

| 5   | Pack  | aging Technologies Research and Development                                                | 219 |

|     | 5.1   | Advanced Packaging Technologies and Designs.                                               |     |

|     | 5.2   | Performance and Reliability of Bonded Interfaces for High-Temperature Packaging            |     |

| 6   | Elect | tric Drive Technologies Materials Research and Development                                 | 242 |

| 6.1         | Power Electronics and Electric Motor Materials Support (Joint with VTO Propulsion Materials)                                                       | .242  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|

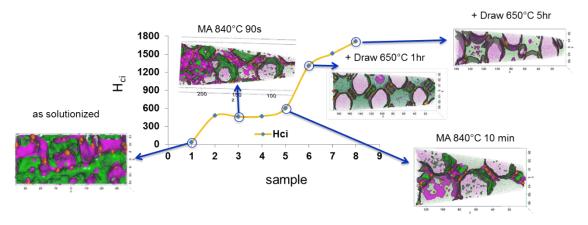

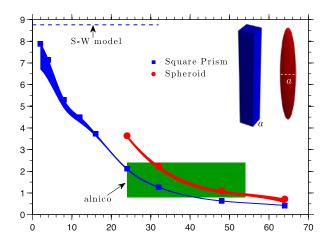

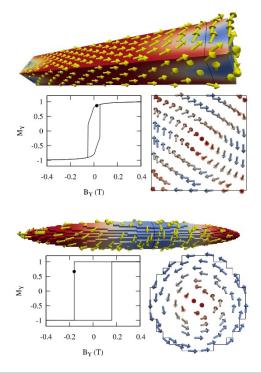

| 6.2         | Development of Radically Enhanced alnico Magnets (DREaM) for Traction Drive Motors                                                                 | .253  |

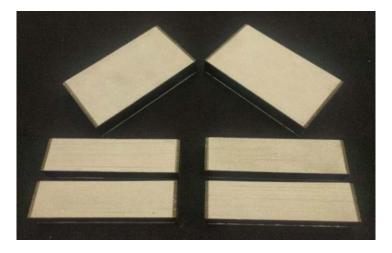

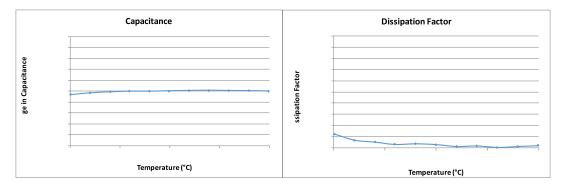

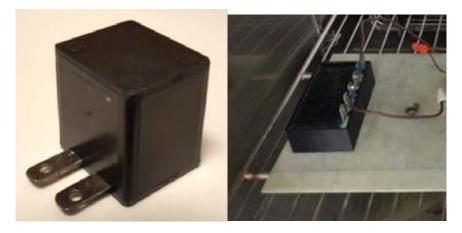

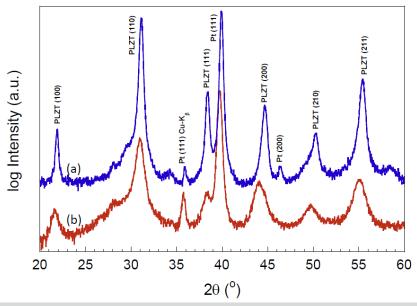

| 6.3         | Multilayered Film Capacitors for Advanced Power Electronics and Electric Motors for Electric Traction Drives                                       |       |

| 6.4         | High Performance DC Bus Film Capacitor                                                                                                             | .273  |

| 6.5         | High Temperature DC Bus Capacitor Cost Reduction & Performance Improvements                                                                        |       |

| 6.6         | Cost-Effective Fabrication of High-Temperature Ceramic Capacitors for Power Inverters                                                              |       |

| 0.0         | Cost-Effective Padrication of Figh-Temperature Ceranic Capacitors for Fower inverters                                                              | . 293 |

| Figures     |                                                                                                                                                    |       |

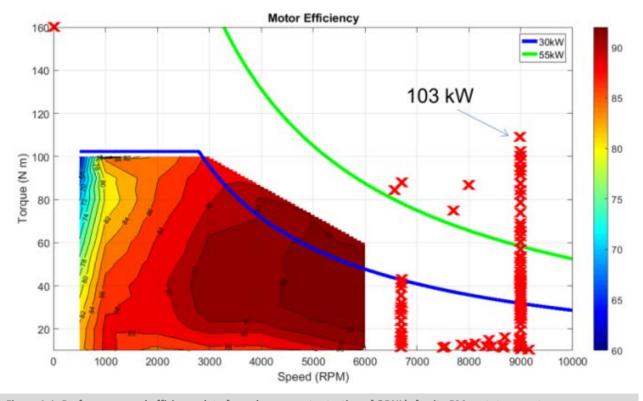

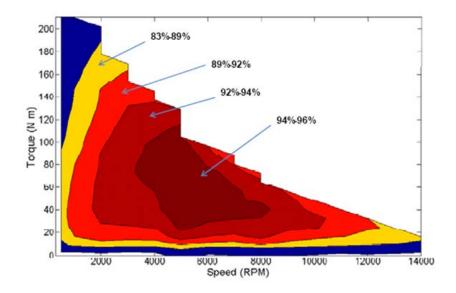

|             | Performance and efficiency data from dynamometer testing of ORNL's ferrite PM                                                                      | 22    |

| Figure 1-2: | prototype motor                                                                                                                                    | 22    |

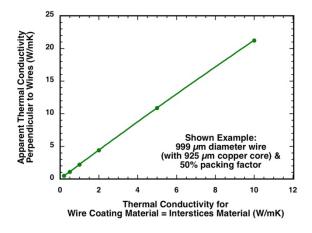

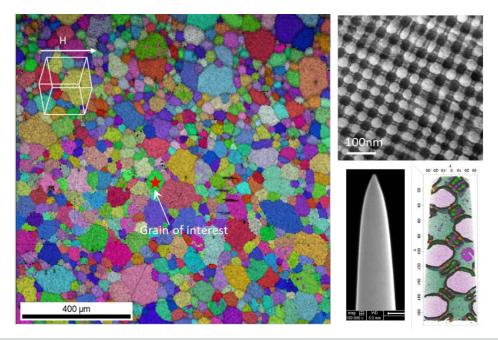

|             | to the wire axis.                                                                                                                                  | 23    |

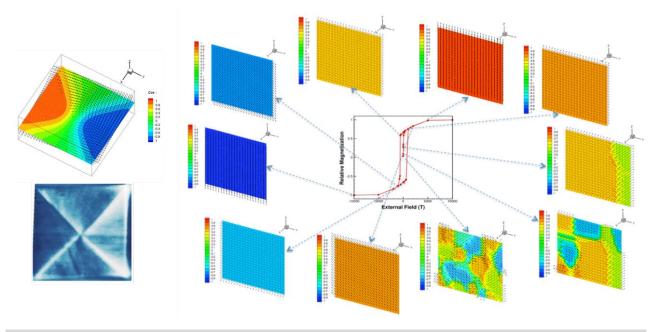

|             | Simulation of a vortex domain structure in iron (top left) and experimentally observed                                                             | 20    |

| •           | vortex structure in iron (bottom left). Simulation of hysteresis loop for a polycrystalline                                                        |       |

|             | grain structure in iron (right)                                                                                                                    | 24    |

|             | Comparison between current metalized polypropylene DC bus capacitor and the                                                                        |       |

|             | developed PML capacitor. Both are rated at 700 µF, but the PML capacitor can handle                                                                |       |

|             | 140°C temperatures, an increase of 35 degrees over current capacitors.                                                                             | 25    |

|             | Comparison between current metalized polypropylene DC bus capacitor and the                                                                        |       |

|             | developed PML capacitor. Both are rated at 700 µF, but the PML capacitor can handle                                                                |       |

| F: 1.6      | 140°C temperatures, an increase of 35 degrees over current capacitors.                                                                             | 26    |

|             | 900V, 1.25mΩ SiC power module with record-low on-state losses, based on new 900V                                                                   | 27    |

|             | SiC MOSFETs                                                                                                                                        | 21    |

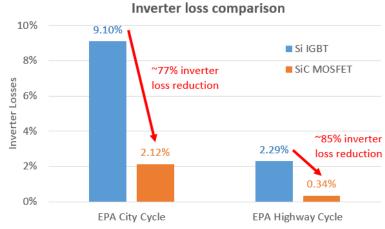

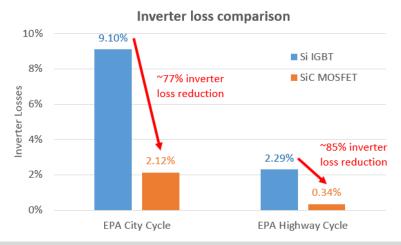

|             | 78% combined inverter loss reduction is possible when using the 900V SiC power modules in place of Si IGBT power modules for a 90kW Ford Focus EV  | 27    |

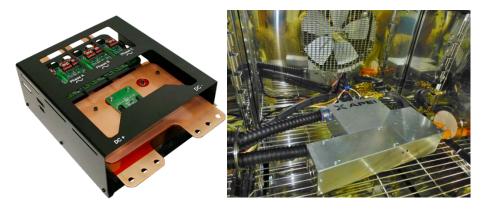

|             | (Left) SiC-based traction drive inverter. (Right) Inverter under test in an environmental                                                          | 21    |

|             | chamber                                                                                                                                            | 28    |

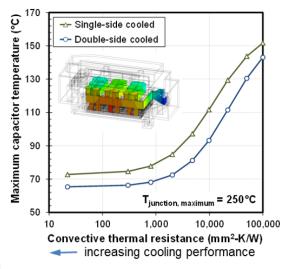

|             | Simulation-predicted capacitor temperatures for a WBG operating condition with results                                                             |       |

|             | showing that electrical interconnection cooling enables capacitor temperatures <85°C for                                                           |       |

|             | WBG device temperatures up to 250°C.                                                                                                               | 29    |

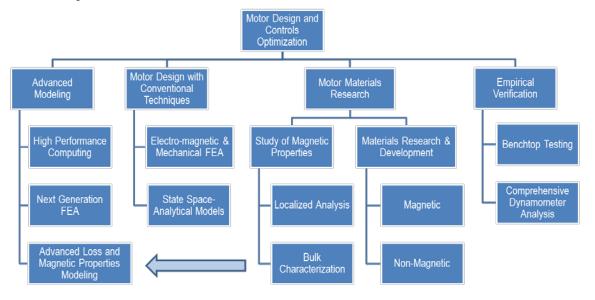

| Figure 2-1: | Motor research thrust areas and project structure.                                                                                                 | 36    |

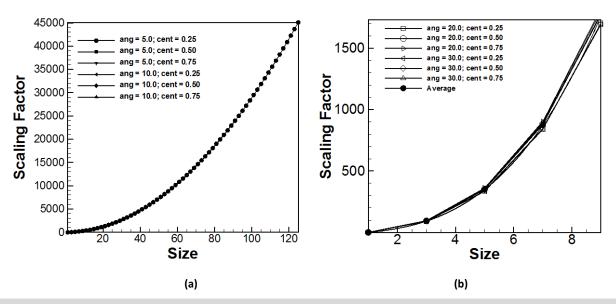

|             | Scaling of the exchange energy (a) and dipole-dipole interaction energy (b) as a function                                                          |       |

|             | of the system size for body-centered cubic iron.                                                                                                   |       |

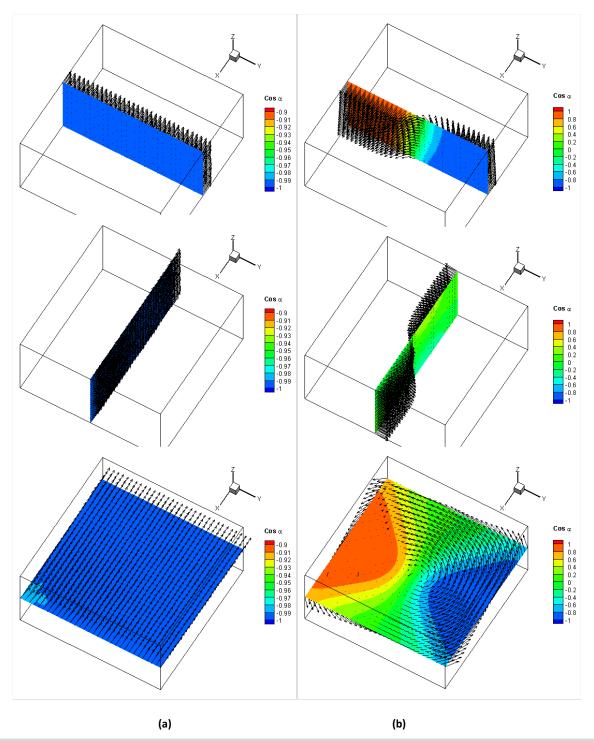

|             | Evolution of the magnetic moment distribution as a function of system size showing the                                                             |       |

|             | transition from monodomain (a) to vortex structure (b). [Note: Size in (a) = $1 (9.152 \times 10^{-2})$                                            | 20    |

|             | $9.152 \times 4.576 \text{ nm}$ and in (b) = $51 (467 \times 467 \times 236.5 \text{ nm}^3)$ .]                                                    | 39    |

| Figure 2-4: | MD simulations of the deformation of Fe-Si single crystals containing 10 to 25 at. % (5 to                                                         | 40    |

| Eiguro 2 5  | 12 wt %) Si at (a) 400 K and (b) 773 K                                                                                                             |       |

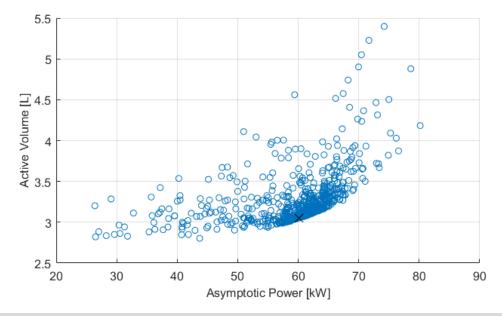

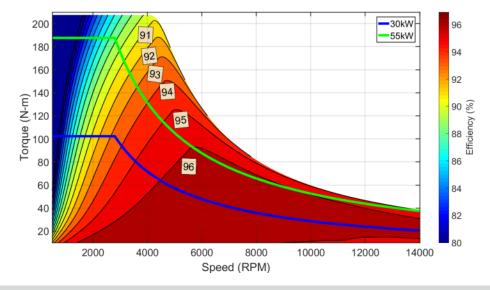

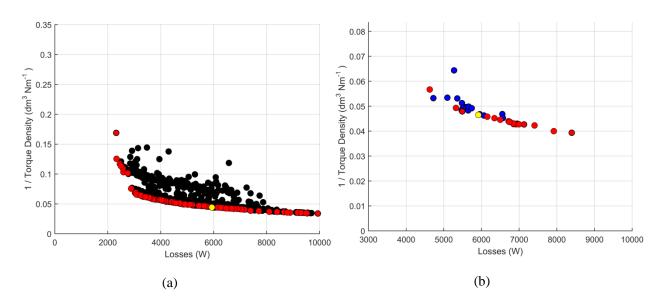

|             | Optimization trend: Volume versus asymptotic power for 1008 candidate designs                                                                      |       |

|             | Optimization trend: Volume versus asymptotic power for 1008 candidate designs Optimization trend: Active volume power density versus active volume |       |

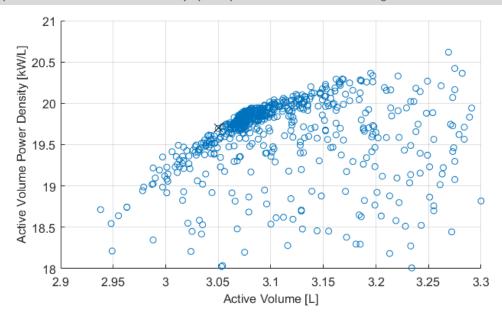

|             | Optimization trend: Active volume power density versus L/D ratio.                                                                                  |       |

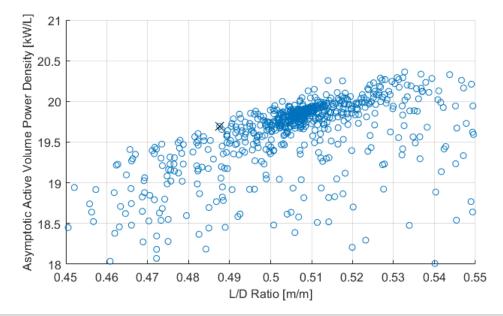

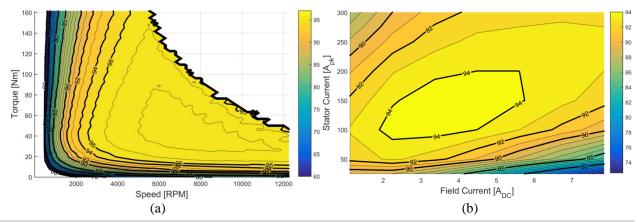

|             | Simulated torque-speed efficiency map.                                                                                                             |       |

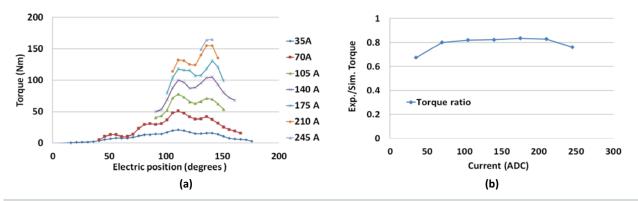

|             | D: Locked rotor torque versus current test results (a) and ratio of experimental and simulated                                                     |       |

|             | results (b)                                                                                                                                        | 46    |

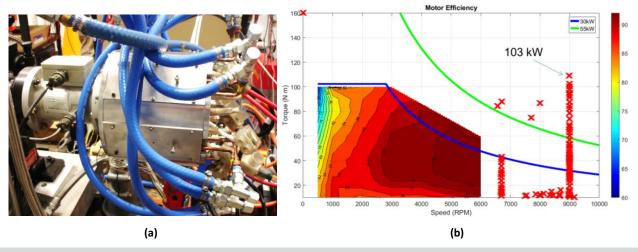

| Figure 2-1  | 1: Ferrite PM prototype on dynamometer (a) and experimental test results (b)                                                                       | 46    |

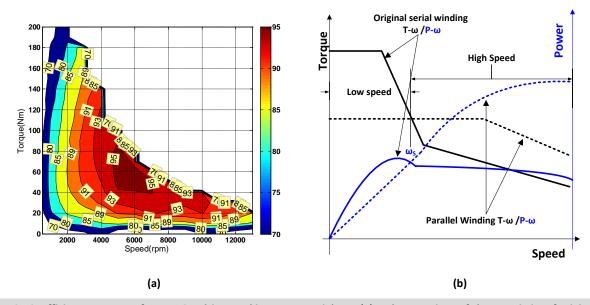

| Figure 2-12 | 2: Efficiency contour of an IPMSM drive used in a commercial HEV (a) and comparison of                                                             |       |

|             | characteristics of original serial and parallel windings of the drive (b).                                                                         | 49    |

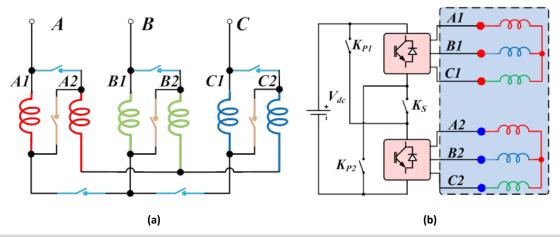

|             | 3: Schematics illustrating two industry patents: (a) Patent 20110234139 A1 (published in                                                           |       |

|             | 2011 by Hsu) and (b) patent B-US20120086380 (published in 2012 by Krieger and Shum)                                                                |       |

| Figure 2-14 | 4: Proposed reconfigurable windings approach.                                                                                                      | 51    |

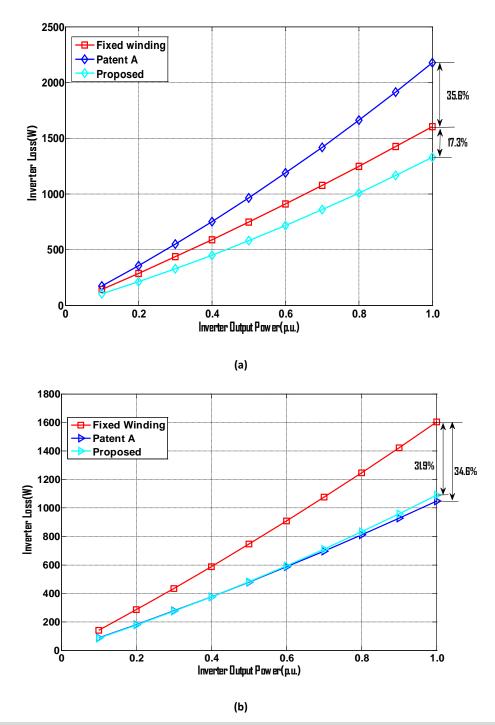

|             | 5: Simulated losses for the proposed design, fixed windings, and patent A system at high speed (a) and low speed (b)                               | 50    |

|             | SDEED VALAND TOW SDEED UD.                                                                                                                         | )2    |

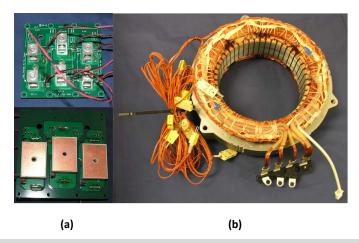

| Figure 2-16: Solid-state ac switch board [(a) top, PCB top view; (a) bottom, PCB bottom view) and        |    |

|----------------------------------------------------------------------------------------------------------|----|

| (b) motor windings used in benchtop test.                                                                | 53 |

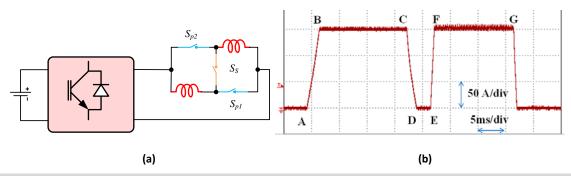

| Figure 2-17: Test circuit diagram with an inverter and three solid-state ac switches (a) and key test    |    |

| waveform of a series to parallel transient, output current 50 A/div, time 5 ms/div (b)                   | 53 |

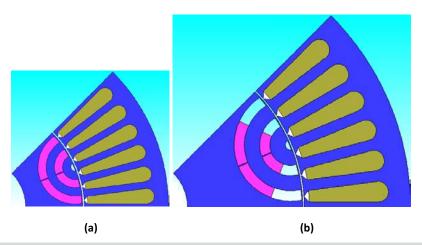

| Figure 2-18: Comparison of two different machine designs with different ratio of characteristic current  |    |

| to rated current: (a) machine design with stack length of 150 mm, stator outer radius of                 |    |

| 100 mm, and $Ic \approx Ir$ ; (b) machine design with stack length of 75 mm, stator outer radius         |    |

| of 141 mm, and $Ic \approx 0.5 Ir$ .                                                                     |    |

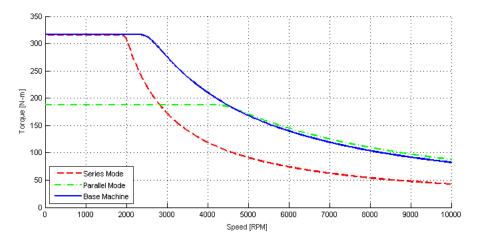

| Figure 2-19: Torque-speed curve demonstrating the performance of both machines                           |    |

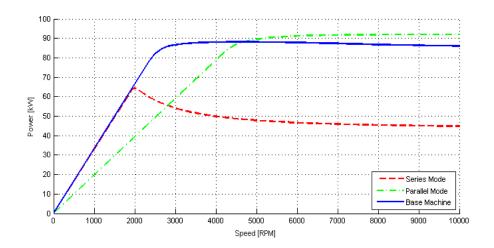

| Figure 2-20: Power-speed curve demonstrating the performance of both machines.                           |    |

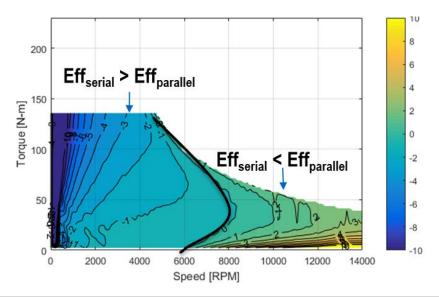

| Figure 2-21: Combined efficiency plot for serial and parallel modes                                      |    |

| Figure 2-22: Differential efficiency plot for serial and parallel modes                                  |    |

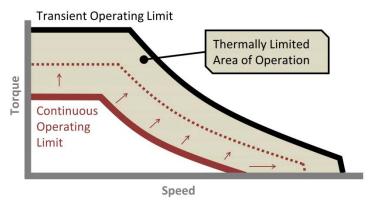

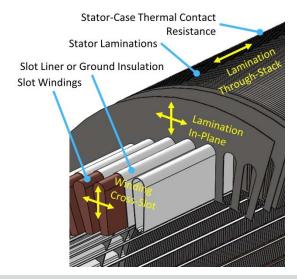

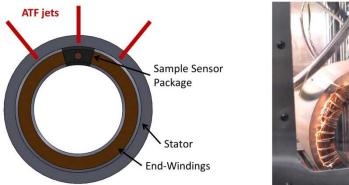

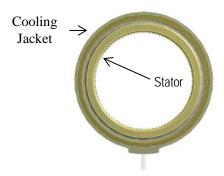

| Figure 2-23: Thermal management impact on motor performance to support increased power                   | 61 |

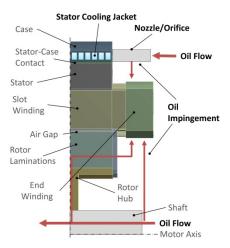

| Figure 2-24: Heat must pass through several layers within the motor to be extracted through active       |    |

| cooling such as through a cooling jacket or spray cooling with oil such as ATF.                          | 62 |

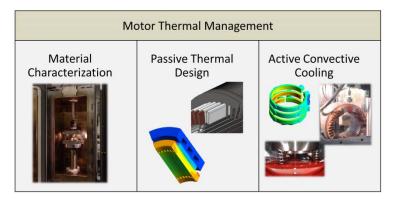

| Figure 2-25: Approach to motor thermal management divided between passive thermal design and             |    |

| active convective cooling                                                                                |    |

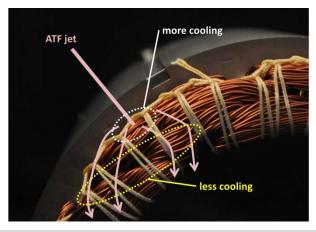

| Figure 2-26: Heat transfer due to ATF jet impingement will vary over the end-winding surface             |    |

| Figure 2-27: Passive stack thermal properties and terminology.                                           |    |

| Figure 2-28: Transverse rupture test apparatus.                                                          | 64 |

| Figure 2-29: Magnet materials (left) being tested for transverse rupture strength within a thermal       |    |

| chamber (right)                                                                                          | 65 |

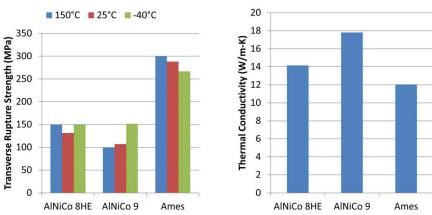

| Figure 2-30: Transverse rupture test results of Ames material and commercial materials (left).           |    |

| Thermal conductivity test results of Ames material compared with commercially available                  |    |

| materials (right)                                                                                        | 65 |

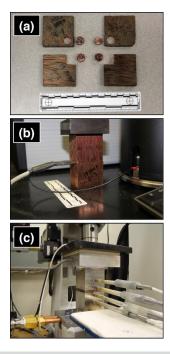

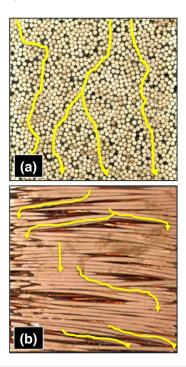

| Figure 2-31: Sample wire bundles in motor slot and end winding (a), winding sample blocks prepared       |    |

| by ORNL for thermal property measurements perpendicular to wire axis (b), winding                        |    |

| sample blocks prepared by ORNL for thermal property measurements parallel to wire                        |    |

| axis (c), test sample under test using transmittance test method (d).                                    | 66 |

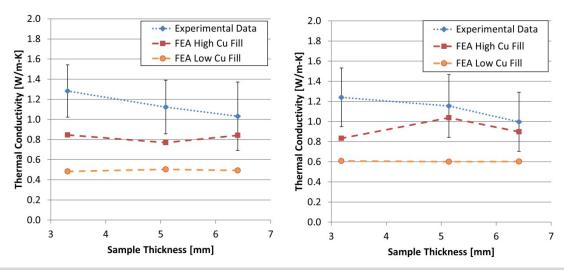

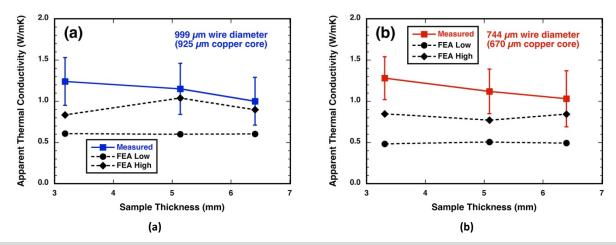

| Figure 2-32: Transmittance test method results for thermal conductivity perpendicular to wire axis,      |    |

| and comparison of experimental data with FEA model results based on low and high                         |    |

| estimates for the sample copper fill factor for 22 AWG (left) and 19 AWG (right)                         |    |

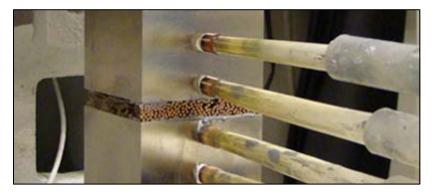

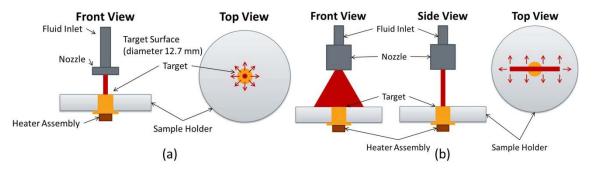

| Figure 2-33: Test setup for circular orifice ATF jet (a). Test setup for planar fan jet (b)              | 67 |

| Figure 2-34: Flow rate of 0.6 L/min led to 58° spray angle (left). Flow rate of 1.0 L/min led to 78°     |    |

| spray angle (right).                                                                                     | 68 |

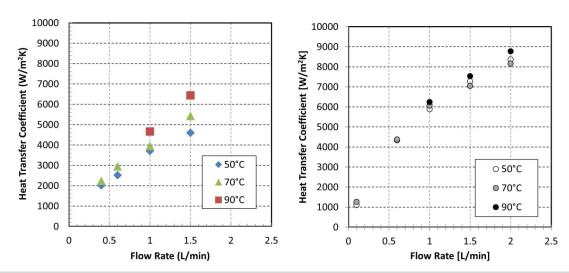

| Figure 2-35: Average heat transfer coefficient versus flow rate measured over 12.7-mm-diameter           |    |

| target surface for planar fan jet (left) and orifice jet (right).                                        | 68 |

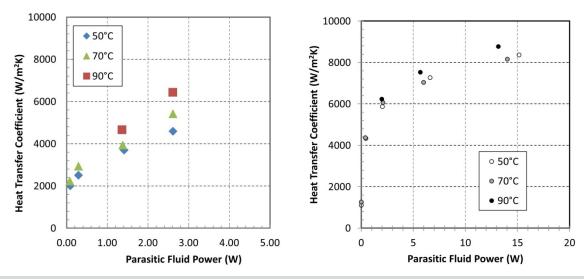

| Figure 2-36: Average heat transfer coefficient versus parasitic power measured over 12.7-mm-             |    |

| diameter target surface for planar fan jet (left) and orifice jet (right).                               | 69 |

| Figure 2-37: Illustration of sensor package installed in end-winding (left), sensor package installed in |    |

| motor and ATF impinging on target surface (right)                                                        | 69 |

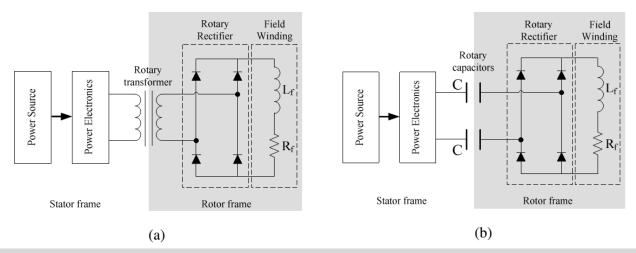

| Figure 2-38: Circuit representation of field coupling for brushless: (a) inductive and (b) inductive     |    |

| couplers                                                                                                 | 73 |

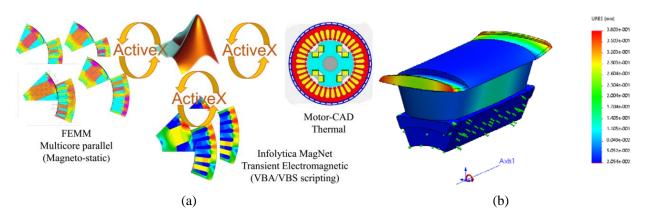

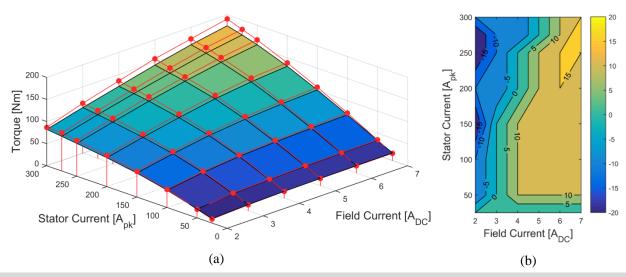

| Figure 2-39: WFSM (a) multi-objective optimization environment with ActiveX software interfaces          |    |

| between solvers and (b) representive rotor stress analysis                                               | 74 |

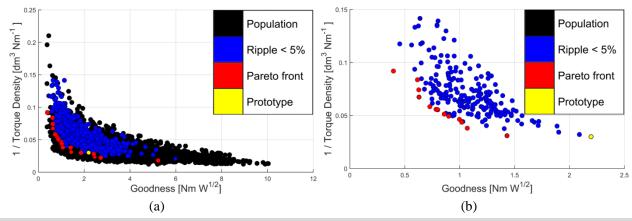

| Figure 2-40: Optimization results for the design of prototypes 1 and 2 shown for the (a) total 7,500     |    |

| member population and (b) designs which meet torque ripple and rotor loss constraints.                   |    |

| The yellow dot indicates the design selected for prototyping                                             | 75 |

| Figure 2-41: Predicted prototypes 1 and 2 efficiency with a winding temperature of 70° C versus (a)      |    |

| speed and torque for peak efficiency and (b) as a function of field and stator currents at the           |    |

| maximum torque angle at 4000 RPM.                                                                        |    |

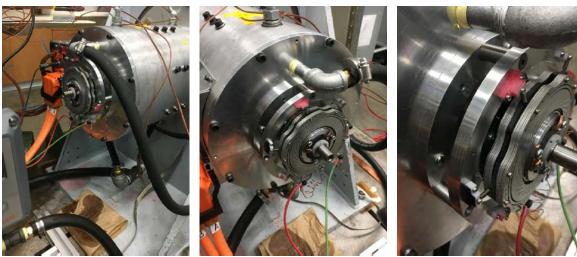

| Figure 2-42: Wound field synchronous machine prototype                                                   | 76 |

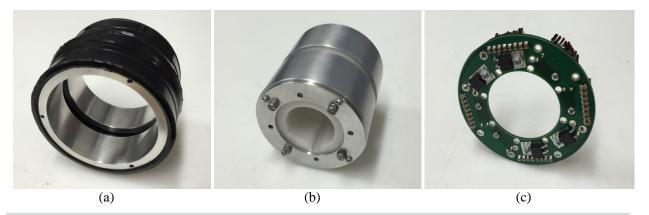

| Figure 2-43: Coupling capacitor stator (a), rotor (b), and rectifier board (c), which comprise the       |    |

| capacitive power coupler assembly                                                                        | 77 |

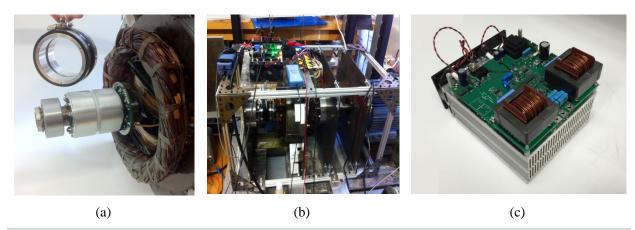

| Figure 2-44: Coupler mounted on WFSM rotor (a), dynamometer test stand (b), and inverter for             |    |

| capacitive power coupling to rotor (c).                                                                  |    |

| Figure 2-45: (left) stator plate, (right) rotor plate.                                                   | 78 |

| Figure 2-46: Photo of the hydroflex plate stack on a small dyne bed                                       | 78  |

|-----------------------------------------------------------------------------------------------------------|-----|

| Figure 2-47: Top - Exploded View of Capacitive Power Coupler (CPC) assembly, Bottom - photos of           |     |

| CPC assembled and installed on WFSM rear shaft                                                            | 79  |

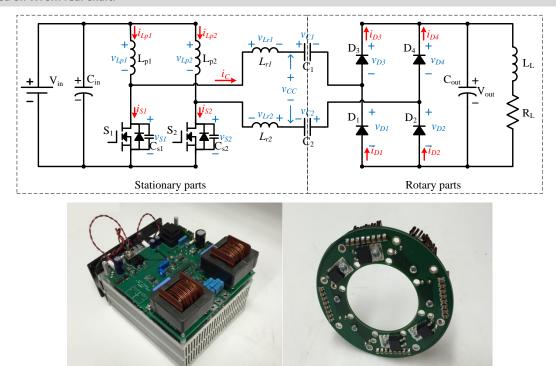

| Figure 2-48: Top - Circuit Schematic for the CPC push-pull class E driver, Bottom - photos of push-       |     |

| pull Class E driver (left) and rotating rectifier board (right)                                           | 79  |

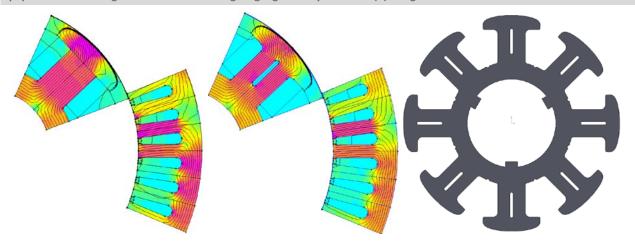

| Figure 2-49: New design optimization for selection of seed design for inclusion of flux barriers; (a)     |     |

| full optimization population with design selected as seed design highlighted in yellow and                |     |

| (b) designs filtered which meet all hard constraints                                                      | 80  |

| Figure 2-50: Base rotor design for extended optimization (left), rotor design selected for prototype 3    |     |

| rotor after adding stress relief filets (center), and lamination design (right)                           | 80  |

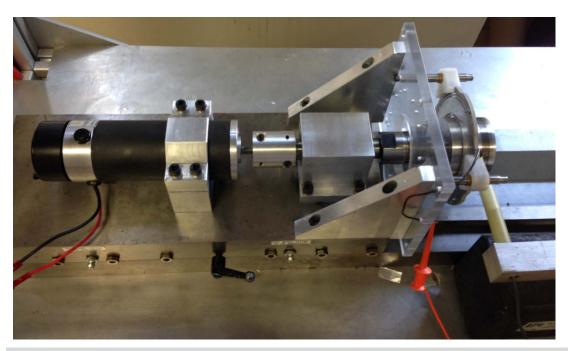

| Figure 2-51: Dynamometer setup during wound field synchronous machine testing with brushes/slip           |     |

| rings                                                                                                     | 81  |

| Figure 2-52: Predicted and measured shaft torque mapping (a) for wound field synchronous motor            |     |

| prototype 2 (The surface is the predicted torque and red dots are measured on                             |     |

| dynamometer) and the (b) maximum torque current angle                                                     | 82  |

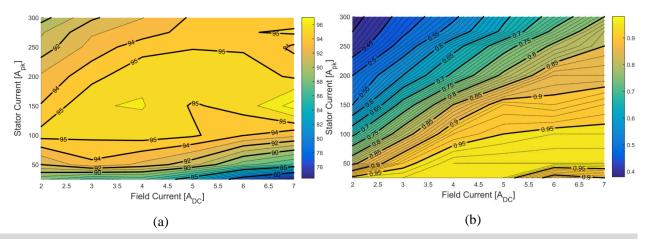

| Figure 2-53: Measured wound field synchronous machine (a) efficiency and (b) power factor at 4000         |     |

| RPM uising Yokogawa PX8000 power analyzer. The temperature of the stator windings                         |     |

| ranged from 45 to 70 °C. The efficiency and power factor maps are for maximum torque                      |     |

| current angles.                                                                                           | 82  |

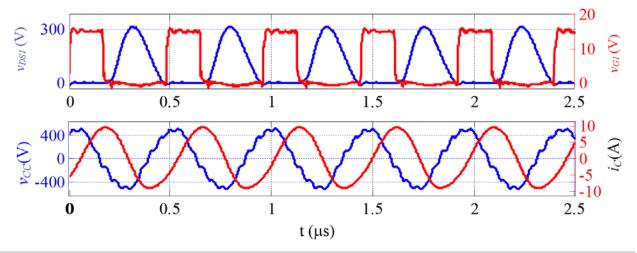

| Figure 2-54: Top - Measured CPC circuit waveforms during 55kW WFSM test. 2MHz switching and               |     |

| 6.5 A rms CPC tank current. *note: labels correspond to circuit diagram.                                  | 83  |

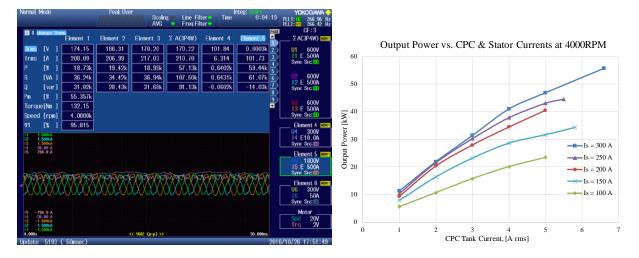

| Figure 2-55: Screen capture of power analyzer during 55kW WFSM test with CPC (left), and WFSM             |     |

| output power verses stator and CPC currents (right).                                                      | 84  |

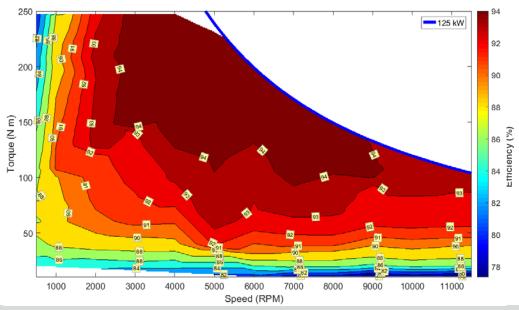

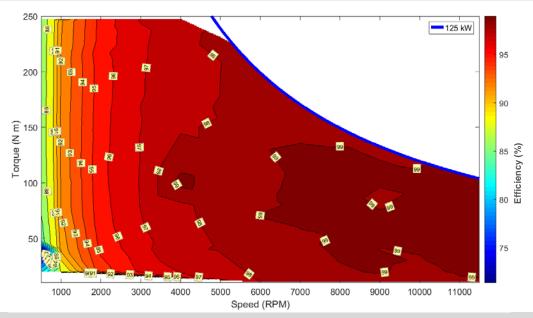

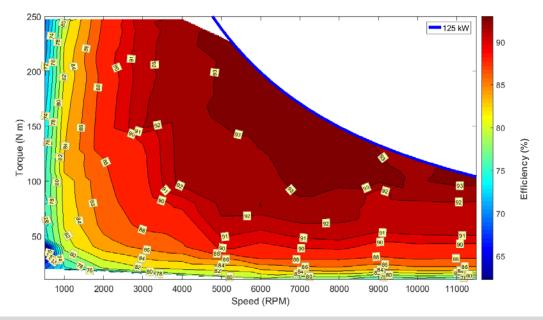

| Figure 2-56: Motor Required Efficiency Map                                                                | 87  |

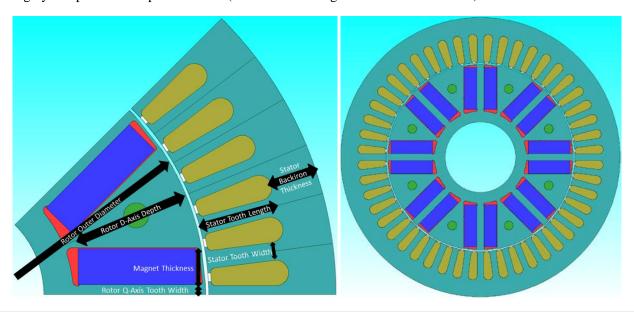

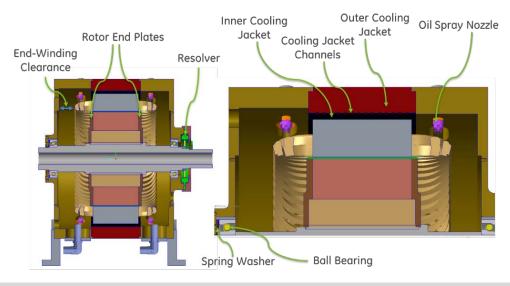

| Figure 2-57: Salient Motor Features Horizontal Cross-Section                                              | 88  |

| Figure 2-58: Carbon Fiber-Wrapped Synchronous Reluctance Rotor and Distributed Winding Stator             |     |

| Hardware                                                                                                  | 89  |

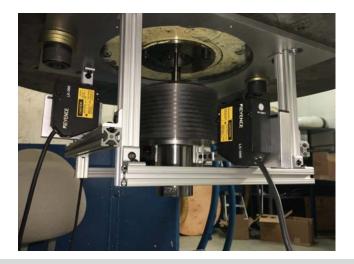

| Figure 2-59: Spin Test Setup                                                                              | 90  |

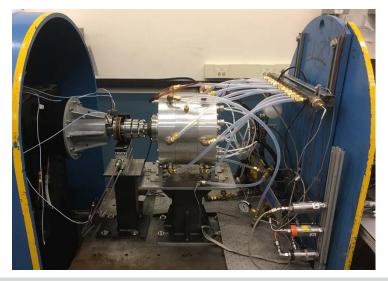

| Figure 2-60: Synchronous Reluctance Motor on Test Stand                                                   |     |

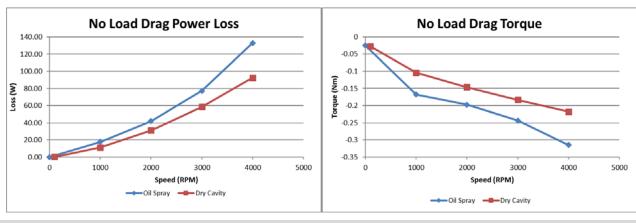

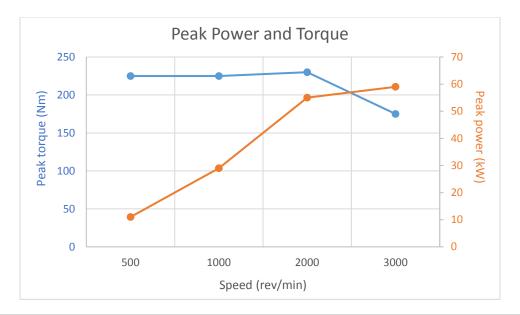

| Figure 2-61: No-Load Drag Torque and Loss                                                                 |     |

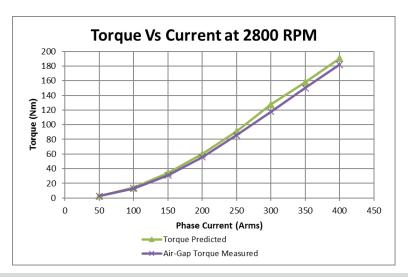

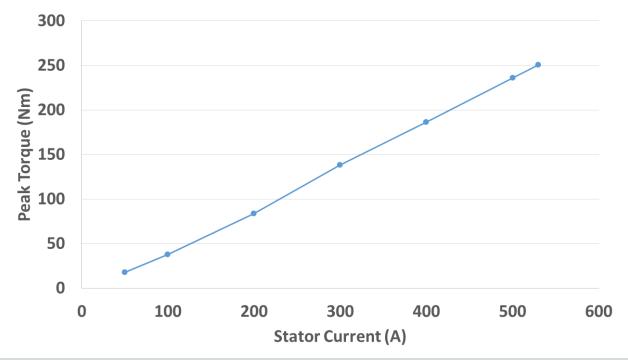

| Figure 2-62: Air-Gap Torque Versus Current.                                                               |     |

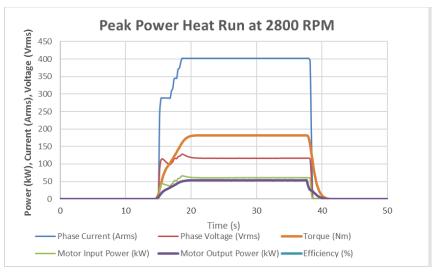

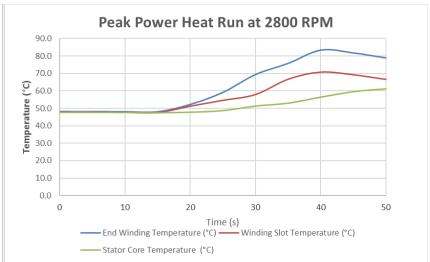

| Figure 2-63: Peak Power Transient Heat Run Results                                                        |     |

| Figure 2-64: Dynamometer Testing Apparatus                                                                |     |

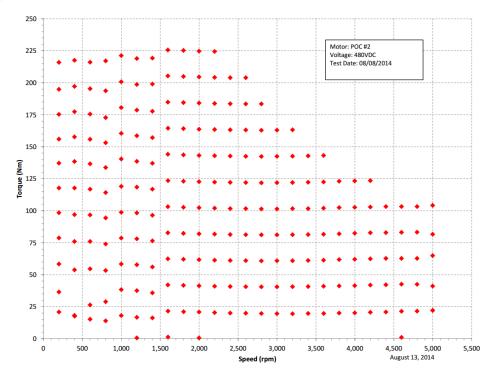

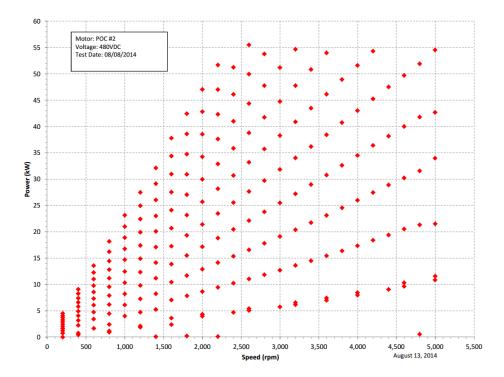

| Figure 2-65: Back EMF POC Motor 1                                                                         |     |

| Figure 2-66: Torque and Power vs. Speed Results                                                           |     |

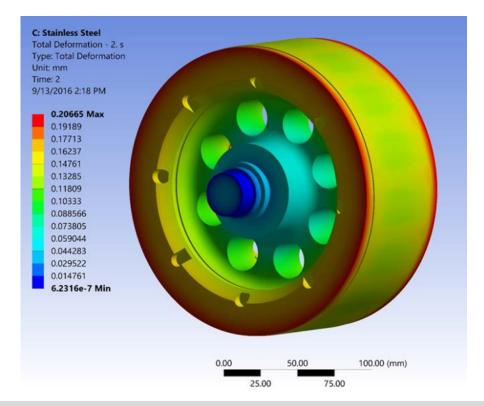

| Figure 2-67: Deformation of the Magnets at 10,000 rpm and 120°C                                           |     |

| Figure 2-68: Magnet Properties of AlNiCo 8HE versus AlNiCo 9                                              |     |

| Figure 2-69: Rotor Assembly                                                                               |     |

| Figure 2-70: POD Estimated Parameter List – Alnico 8HE Magnets                                            |     |

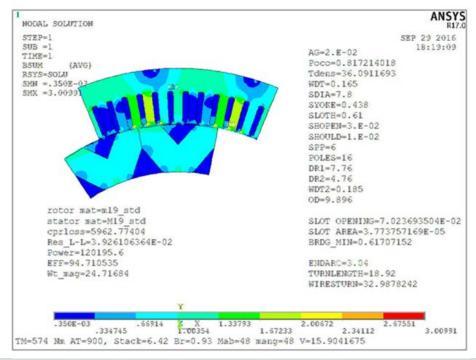

| Figure 2-71: 120 kW ANSYS Solution                                                                        | 100 |

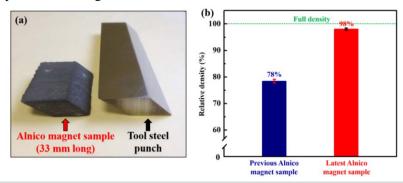

| Figure 2-72: (a) Half-length Alnico magnet sample next to tool steel punch, (b) Relative density of       |     |

| two sintered AlNiCo magnet samples                                                                        | 101 |

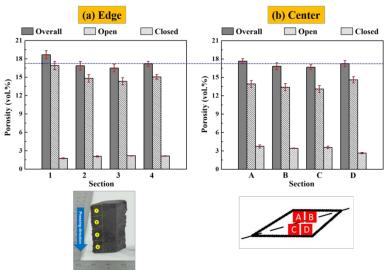

| Figure 2-73: (a) Porosity variations along the pressing direction, (b) porosity data of the edge sections |     |

| vs. compared to center sections                                                                           | 101 |

| Figure 2-74: One Pass (sinter/solution heat treat/quench) Furnace System Ames Laboratory                  |     |

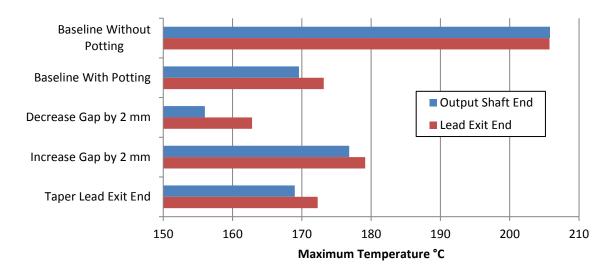

| Figure 2-75: Full CFD model (top) and FEA section model (bottom).                                         |     |

| Figure 2-76: Summary of Material Sensitivity Study                                                        |     |

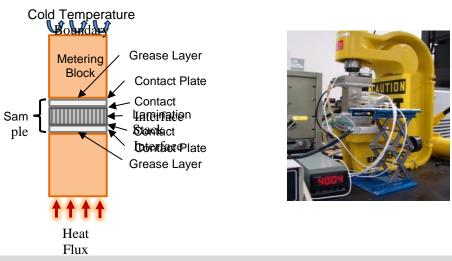

| Figure 2-77: Schematic of ASTM Setup and Test Apparatus                                                   |     |

| Figure 2-78: Motor Stator Thermal Test Bench.                                                             |     |

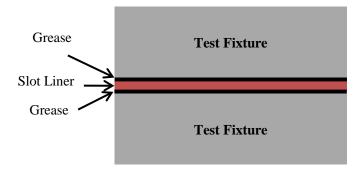

| Figure 2-79: Slot Liner in Test Fixture                                                                   |     |

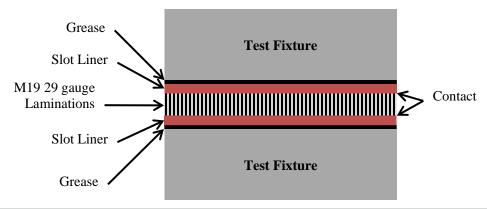

| Figure 2-80: Stack-up to Measure Slot Liner to Stator Thermal Contact Resistance                          |     |

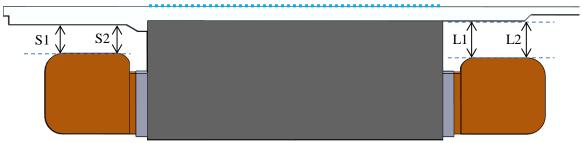

| Figure 2-81: Geometry for FEA Thermal Analysis                                                            |     |

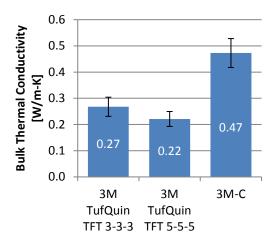

| Figure 2-82: Slot Liner Insulation Thermal Conductivity Results                                           | 106 |

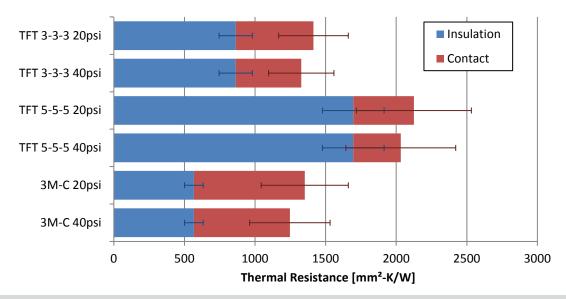

| Figure 2-83: Slot Liner Thermal resistance with Slot Liner to Stator Contact Thermal Resistance           |     |

| Stacked                                                                                                   |     |

| Figure 2-84: FEA results summary                                                                          |     |

| Figure 2-85: ORNL Test Results From POC Motor 2                                                           | 108 |

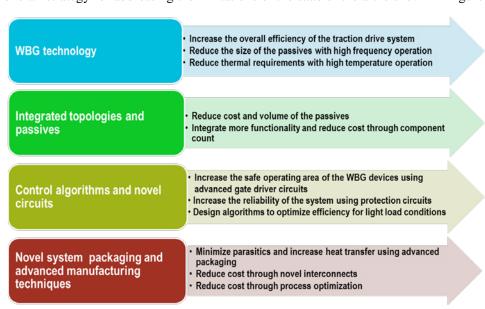

| Figure 3-1: Overall strategy to address limitations of the state of the art.                                                                                                                        |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3-2: Specific approach to address limitations of the state of the art.                                                                                                                       | 112 |

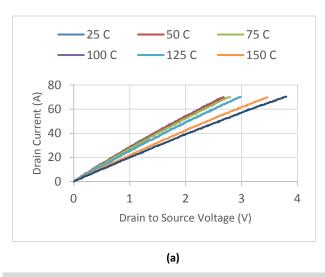

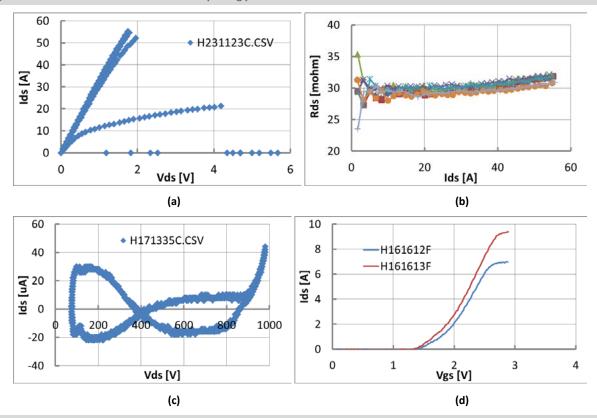

| Figure 3-3: Temperature-dependent output characteristics of 600 V trench-type SiC MOSFETs (a) and                                                                                                   |     |

| 900 V SiC DMOSFETs (b)                                                                                                                                                                              | 113 |

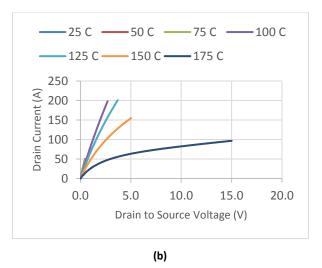

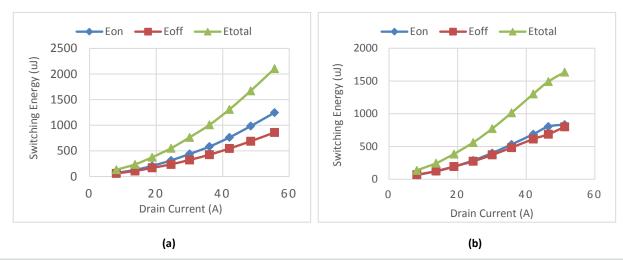

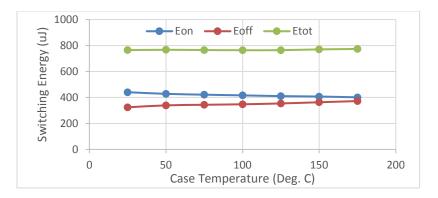

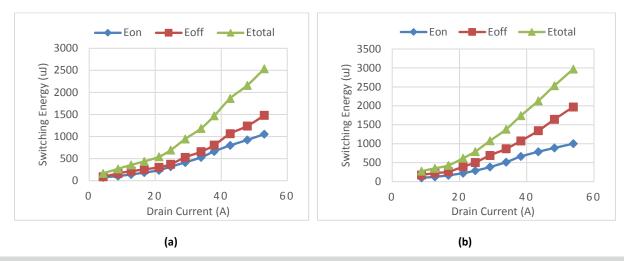

| Figure 3-4: Turn-on and turn-off switching energies for a 650 V trench-type SiC MOSFET at 25°C and 400 V (a) and at 175°C and 400 V (b)                                                             | 113 |

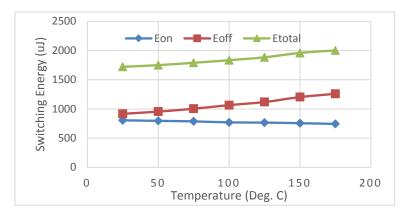

| Figure 3-5: Switching energy as a function of temperature for a 650 V trench-type SiC MOSFET at 400 V                                                                                               |     |

| Figure 3-6: Turn-on and turn-off switching energies for a 900 V SiC DMOSFET at 25°C and 600 V  (a) and 175°C and 600 V (b).                                                                         |     |

| Figure 3-7: Switching energy as a function of temperature for a 900 V SiC DMOSFET at 600 V.                                                                                                         |     |

| Figure 3-7. Switching energy as a function of temperature for a 900 v Sic Diviosite 1 at 600 v                                                                                                      |     |

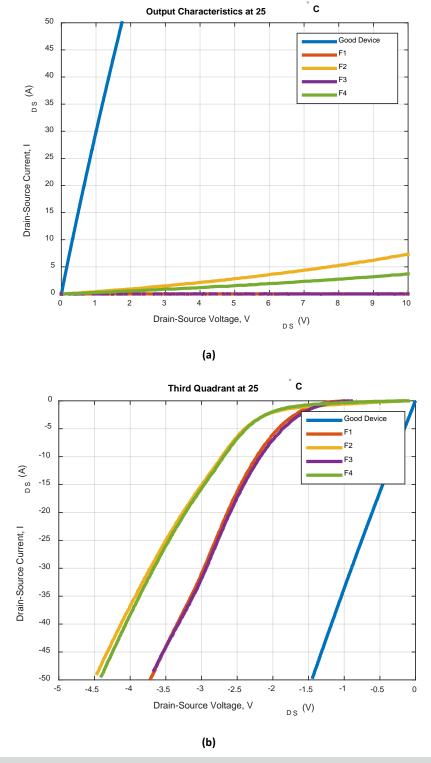

| Figure 3-9: Comparison among failed devices: output characteristics (a) and third quadrant                                                                                                          | 113 |

| characteristics (b). F1 = protected short circuit test conducted at 75°C, F2 = unprotected                                                                                                          |     |

| short circuit test conducted at 75°C, F3 = protected short circuit test conducted at 100°C,                                                                                                         |     |

| and F4 = unprotected short circuit test conducted at 100°C                                                                                                                                          | 116 |

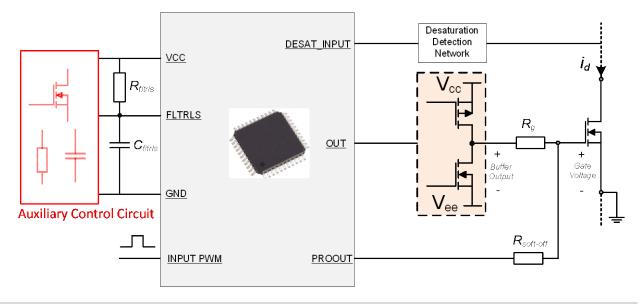

| Figure 3-10: Commercial gate drive chip with auxiliary control circuit                                                                                                                              |     |

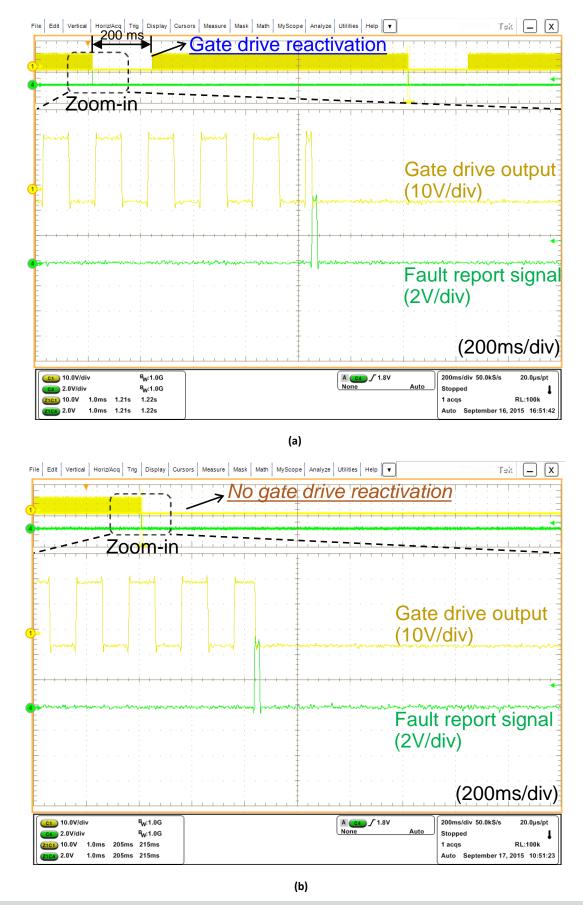

| Figure 3-11: Desaturation protection mode without auxiliary control circuit (a) and with auxiliary                                                                                                  | 117 |

| control circuit (b).                                                                                                                                                                                | 118 |

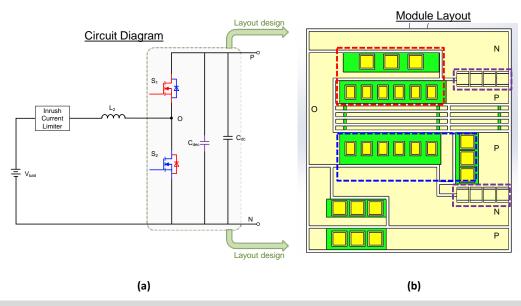

| Figure 3-12: Boost converter diagram (a) and DBC layout design of the power module (b)                                                                                                              |     |

| Figure 3-13: Power loop parasitic inductance of the boost module                                                                                                                                    | 120 |

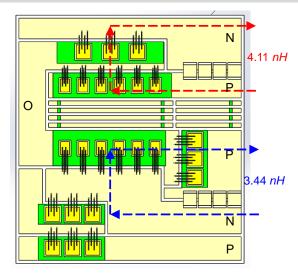

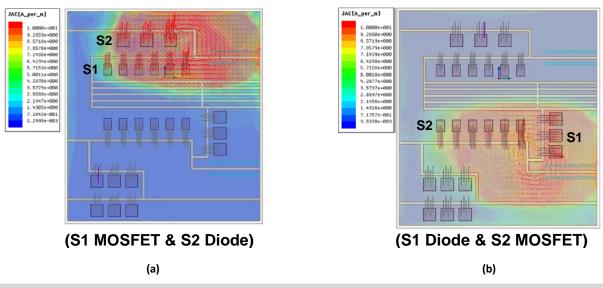

| Figure 3-14: Current distribution of the boost module: S1 MOSFET and S2 diode (a) and S1 diode and                                                                                                  | 120 |

| S2 MOSFET (b).                                                                                                                                                                                      | 121 |

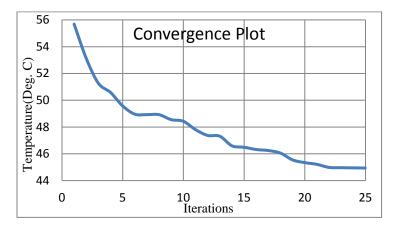

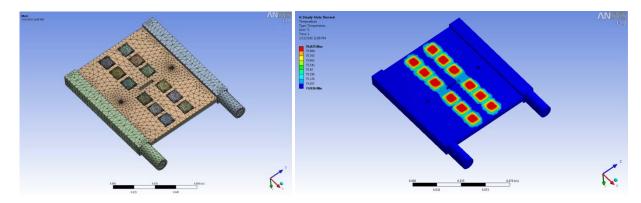

| Figure 3-15: Convergence plot of the heat sink optimization.                                                                                                                                        |     |

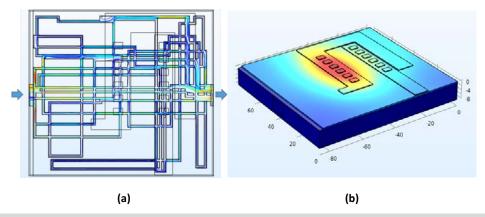

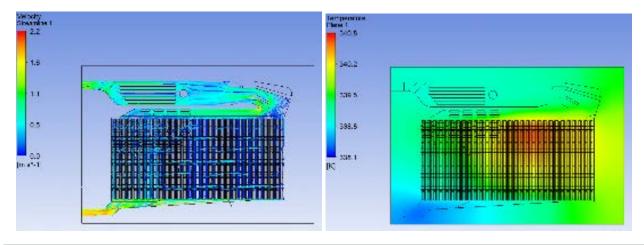

| Figure 3-16: Simulation results for the optimized heat sink: streamline plot (a) and temperature                                                                                                    |     |

| distribution (b).                                                                                                                                                                                   | 122 |

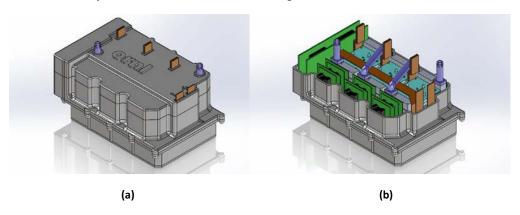

| Figure 3-17: Conceptual 3-D drawing of the 30 kW three-phase liquid-cooled inverter: overview (a)                                                                                                   |     |

| and uncovered view (b).                                                                                                                                                                             | 122 |

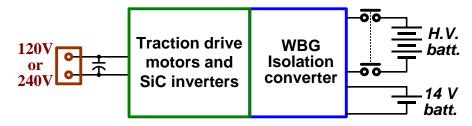

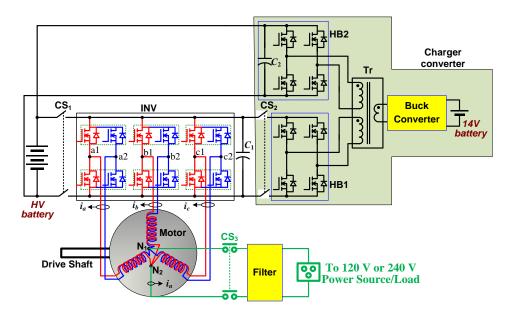

| Figure 3-18: Conceptual diagram of an integrated OBC.                                                                                                                                               |     |

| Figure 3-19: Proposed integrated OBC using a three-port isolation converter                                                                                                                         |     |

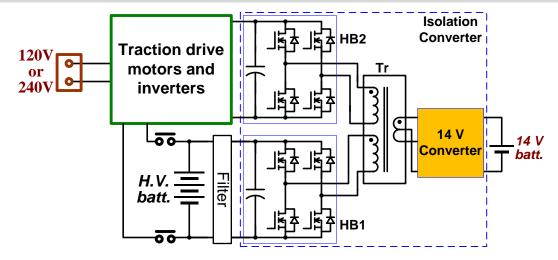

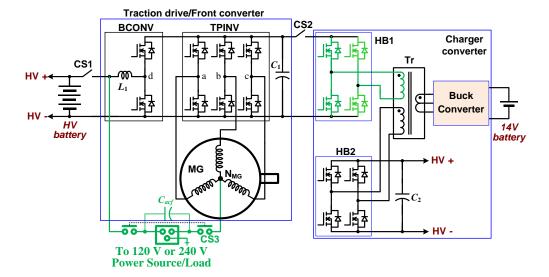

| Figure 3-20: Integrated OBC applied to traction drive system with dual inverter and motor                                                                                                           | 127 |

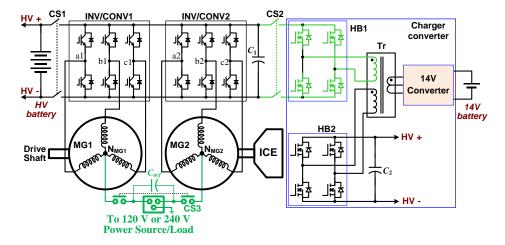

| Figure 3-21: Integrated OBC applied to a segmented traction drive.                                                                                                                                  |     |

| Figure 3-22: Integrated OBC applied to traction drive system with a boost converter                                                                                                                 | 128 |

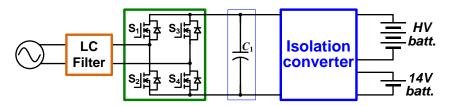

| Figure 3-23: The isolation converter applied to a stand-alone OBC                                                                                                                                   | 128 |

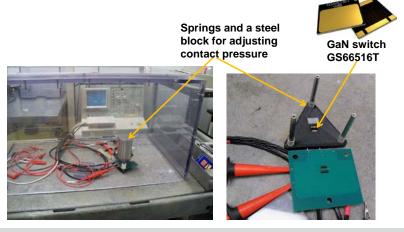

| Figure 3-24: Static characterization test setup using pressure contacts.                                                                                                                            | 129 |

| Figure 3-25: Static characterization test results: (a) I-V curves as the gate source voltage (Vgs) stepped from 0.5 V to 6.5 V in increments of 1 V, (b) spread of on-resistance [Rds(on)] of eight |     |

| samples at $Vgs = 6.5 \text{ V}$ , (c) breakdown voltage, and (d) gate threshold voltage                                                                                                            | 129 |

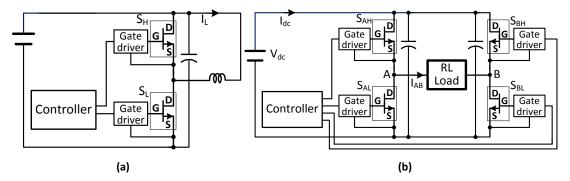

| Figure 3-26: Pulse and H-bridge converter test circuits [(a) and (b), respectively] for the GaN Systems                                                                                             |     |

| devices                                                                                                                                                                                             |     |

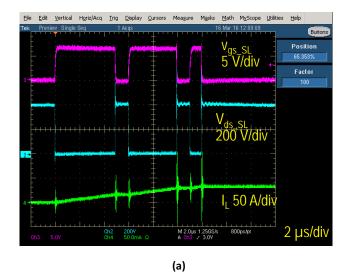

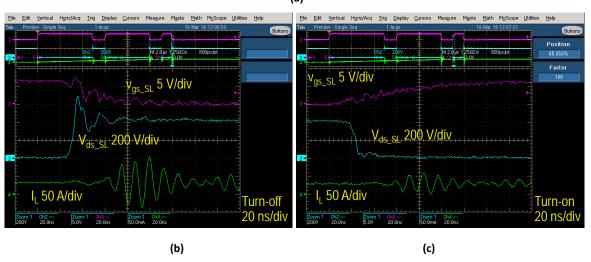

| Figure 3-27: Pulse test results: (a) pulse test waveforms, (b) turn-off, and (c) turn-on.                                                                                                           | 130 |

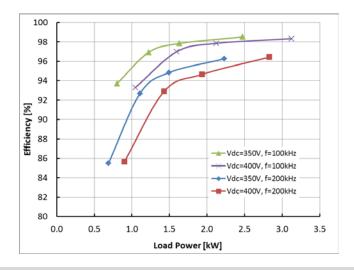

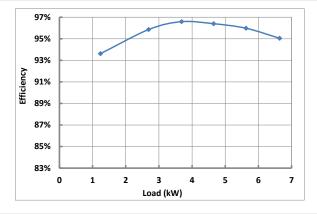

| Figure 3-28: GaN H-bridge converter test results on efficiency vs. load power at different frequencies                                                                                              |     |

| and dc bus voltages.                                                                                                                                                                                | 130 |

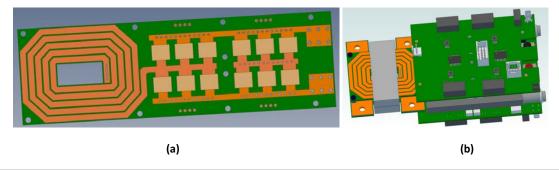

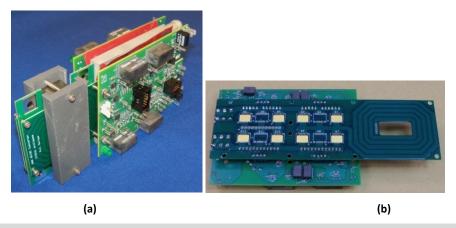

| Figure 3-29: Final design for the 6.6 kW GaN-based three-port isolation converter: (a) PCB for planar                                                                                               | 101 |

| transformer winding and GaN power plane board and (b) complete assembly.                                                                                                                            |     |

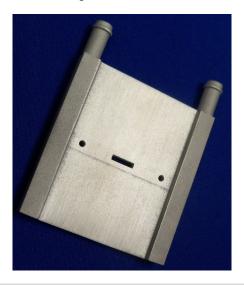

| Figure 3-30: 3-D printed aluminum pin fin cold plate.                                                                                                                                               | 131 |

| Figure 3-31: Finite element analysis results for the 3-D-printed cold plate                                                                                                                         | 131 |

| Figure 3-32: Photos of (a) the 6.6 kW GaN isolation converter prototype and (b) the assembled power                                                                                                 | 100 |

| and gate drive boards.                                                                                                                                                                              |     |

| Figure 3-33: Digital signal processor board using the latest Texas Instruments dual-core chip                                                                                                       |     |

| Figure 3-34: GaN isolation converter test setup.                                                                                                                                                    | 132 |

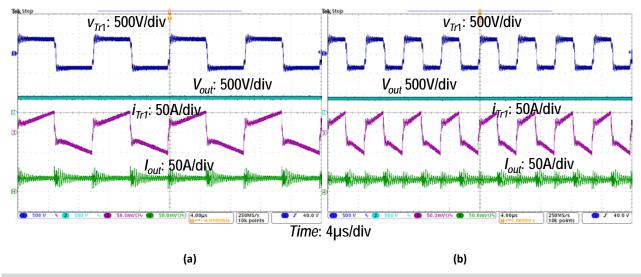

| Figure 3-35: GaN isolation converter test results showing operating waveforms (a) at fsw = 100 kHz                                                                                                  | 122 |

| and (b) at fsw = 200 kHz.                                                                                                                                                                           |     |

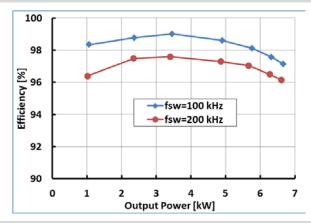

| Figure 3-36: GaN isolation converter test results showing measured GaN converter efficiency                                                                                                         | 155 |

|                                                                                                                                                                                                     | 124 |

| drive                                                                                                                                                                                               | 134 |

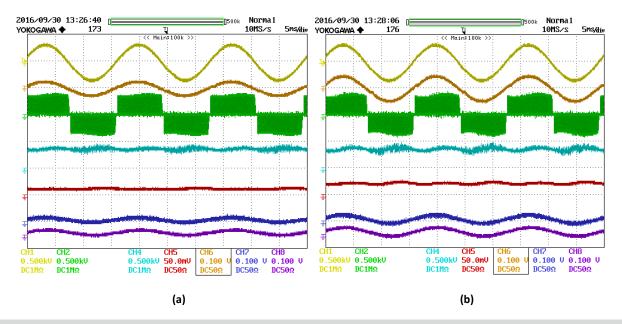

| Figure 3-38: Test results—typical operating waveforms for the integrated onboard charger system at    |     |

|-------------------------------------------------------------------------------------------------------|-----|

| charging power levels of (a) 3.6 kW and (b) 6.6 kW                                                    | 134 |

| Figure 3-39: Integrated onboard charger system test results showing measured system efficiency at     | 124 |

| grid voltage of 240 V.                                                                                | 134 |

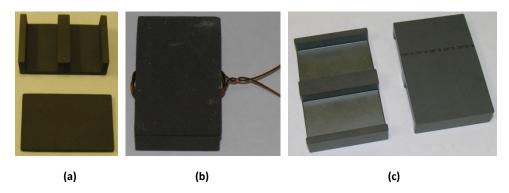

| Figure 3-40: Photos of the ORNL printed cores (a) and inductor (b) and commercial ferrite cores (c)   | 105 |

| for comparison.                                                                                       | 135 |

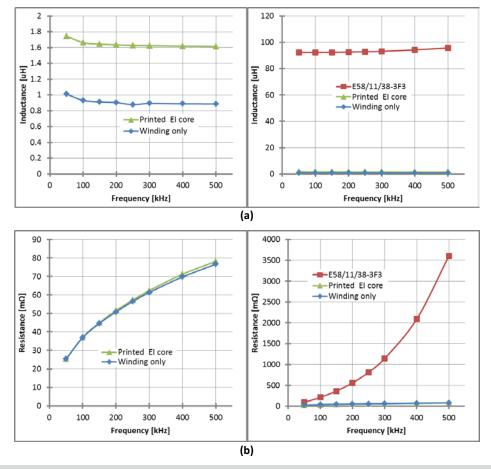

| Figure 3-41: Measured inductance (a) and resistance (b) of the inductor using the printed cores or an |     |

| air core and an inductor using a commercial ferrite core.                                             | 135 |

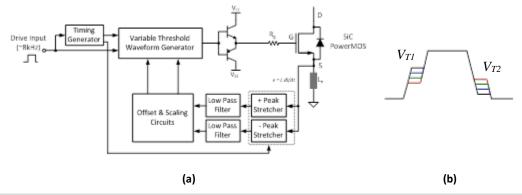

| Figure 3-42: AGD circuit topology selected for COTS implementation incorporating WBG source           |     |

| inductive current sensing for di/dt feedback control (a) and the associated variable                  |     |

| threshold gate drive waveform produced (b).                                                           | 140 |

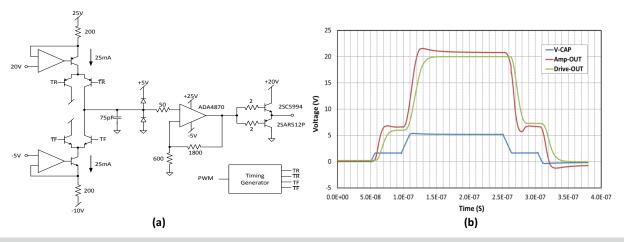

| Figure 3-43: Version 1 waveform generator block diagram (a) and PSpice simulation output              |     |

| waveform (b)                                                                                          | 141 |

| Figure 3-44: Timing generator PSpice simulation using circuit models from a modern integrated         |     |

| circuit process.                                                                                      |     |

| Figure 3-45: ECL-based timing generator PCB for the initial waveform generator design                 | 142 |

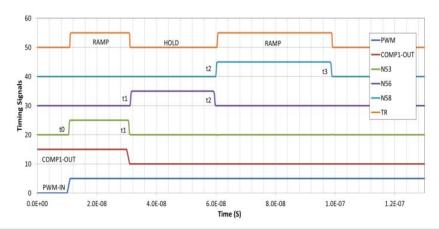

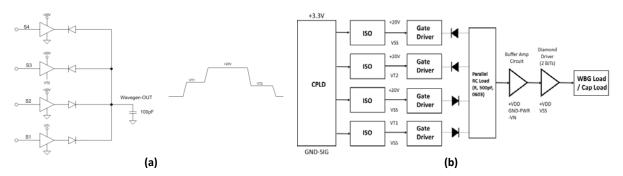

| Figure 3-46: Alternative waveform generator (WaveGen2) simplified functional diagram (a) and          |     |

| overall circuit block diagram (b)                                                                     | 142 |

| Figure 3-47: Fabricated WaveGen2 waveform generator module                                            | 143 |

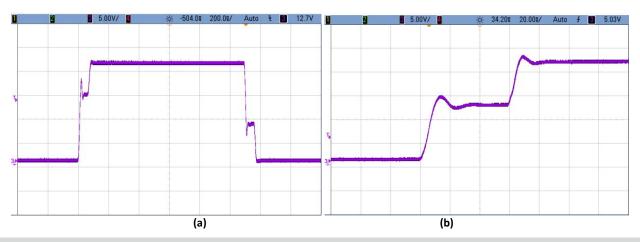

| Figure 3-48: WaveGen2 Measured Waveforms: Rising and falling edges showing the two variable           |     |

| threshold values (a) and a zoom view of a rising edge showing ~7ns and ~5ns rise times in             |     |

| the two transition regions (b).                                                                       | 143 |

| Figure 3-49: AGD Feedback PCB used in AGD benchtop system testing                                     | 143 |

| Figure 3-50: Benchtop prototype AGD composed of the WaveGen2, feedback, and clamped inductor          |     |

| modules (a) and close-up view of SiC Power MOS device with added source lead                          |     |

| inductance (b)                                                                                        | 144 |

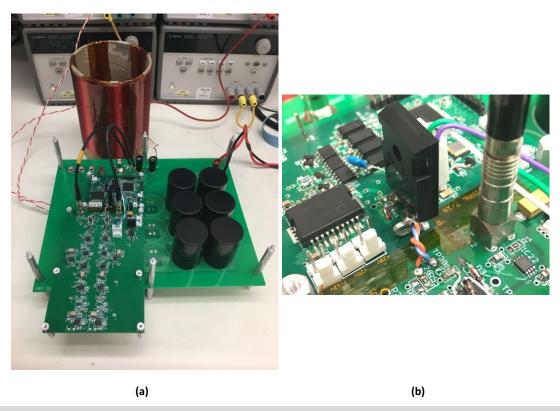

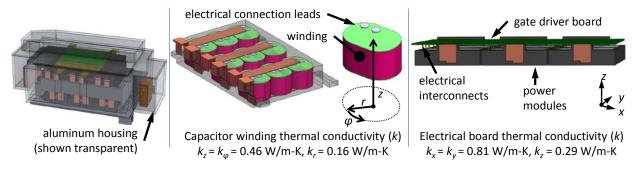

| Figure 3-51: CAD drawing of 2012 LEAF inverter (left), DC-link capacitor (middle), and power          |     |

| module-gate driver assembly (right). Anisotropic thermal conductivity properties were                 |     |

| used to model the thermal performance of the capacitor windings and gate driver board                 | 148 |

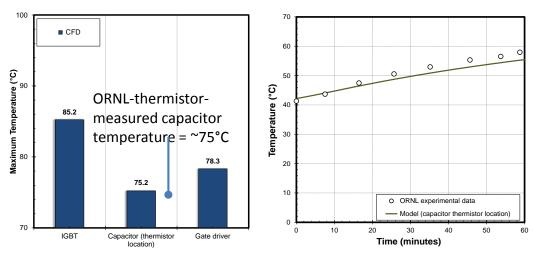

| Figure 3-52: CFD-computed temperatures for the steady-state 80 kW operating condition (left) and      |     |

| transient FEA-generated capacitor temperature response for the 50 kW operating condition              |     |

| (right). Both the steady-state and transient model results compared well with                         |     |

| experimentally obtained data from ORNL [1].                                                           | 150 |

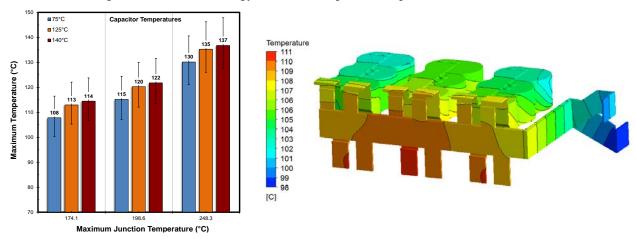

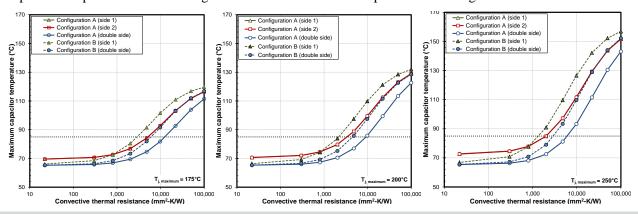

| Figure 3-53: CFD-computed maximum capacitor winding temperatures for MOSFET temperatures of           |     |

| 175°C, 200°C, and 250°C (left). The under-hood temperatures are provided in the plot                  |     |

| legend. CFD-computed DC bus bar and capacitor winding temperatures (right). Results                   |     |

| demonstrate that heat is conducted from the power modules to the capacitors via the bus               |     |

| bars                                                                                                  | 151 |

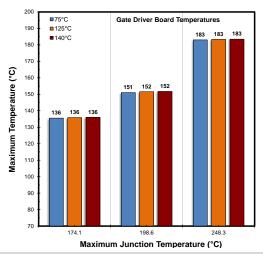

| Figure 3-54: CFD-computed maximum gate driver temperatures for MOSFET temperatures of 175°C,          |     |

| 200°C, and 250°C. The under-hood temperatures are provided in the plot legend                         | 152 |

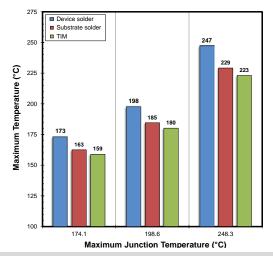

| Figure 3-55: CFD-computed maximum solder and TIM temperatures for MOSFET temperatures of              |     |

| 175°C, 200°C, and 250°C.                                                                              | 152 |

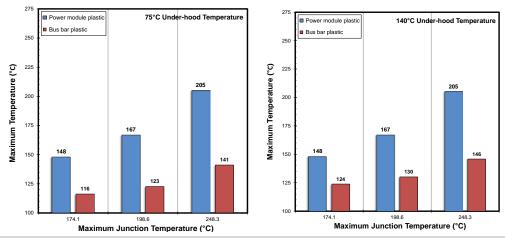

| Figure 3-56: CFD-computed maximum power module and bus bar molding plastic temperatures for           |     |

| MOSFET temperatures of 175°C, 200°C, and 250°C. Results for under-hood ambient                        |     |

| temperatures of 75°C (left) and 140°C (right) are provided.                                           | 152 |

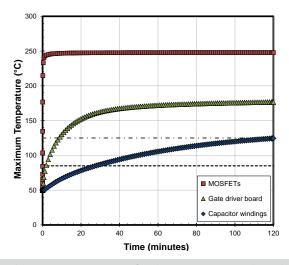

| Figure 3-57: Transient FEA-estimated temperature response for the MOSFETs, gate driver board, and     | 102 |

| capacitors.                                                                                           | 153 |

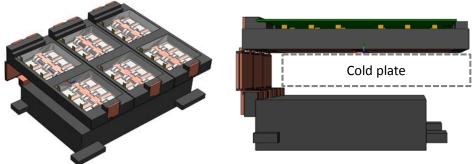

| Figure 3-58: CAD drawing of the modified LEAF inverter used to evaluate various capacitor cooling     | 100 |

| strategies. This modified configuration would enable placing a cold plate between all                 |     |

| components to aid in cooling the capacitors (right).                                                  | 153 |

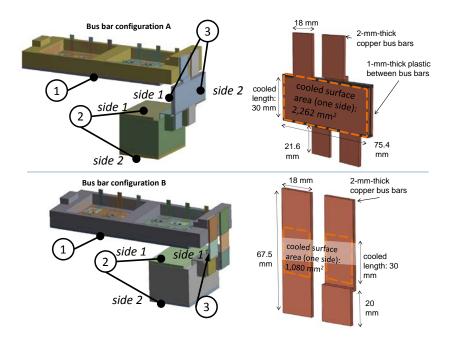

| Figure 3-59: Bus bar Configurations A (top) and B (bottom). FEA was conducted to evaluate three       | 133 |

| capacitor cooling strategies: 1) increased cooling on the power module cold plate, 2) using           |     |

| cold plates on one or both sides of the capacitor, and 3) using cold plates on one or both            |     |

| sides of the DC bus bars                                                                              | 154 |

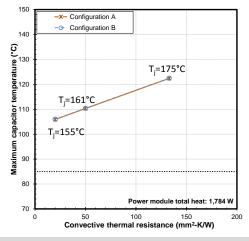

| Figure 3-60: Maximum capacitor temperatures versus the power module cold plate convective             | 154 |

| resistance. Reducing the power module convective resistance from 133 mm <sup>2</sup> -K/W to          |     |

| 20 mm <sup>2</sup> -K/W reduces the capacitor maximum temperature by ~17°C                            | 154 |

| 20 mm2 is it reduces the capacitor maximum temperature by 1/ C                                        | т   |

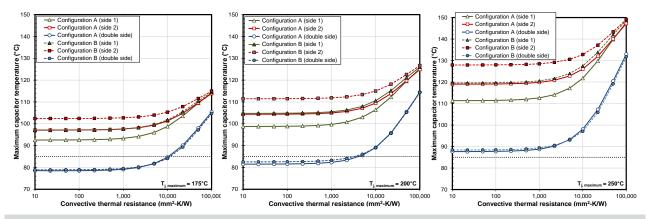

| Figure 3-61: Maximum capacitor temperatures plotted versus the capacitor cold plate convective                                                                                                |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| thermal resistance. The 175°C, 200°C, and 250°C junction temperature case results are                                                                                                         |       |

| provided. Results show that using two cold plates on the capacitor can enable the capacitor                                                                                                   |       |

| to operate below 85°C for junction temperatures up to 200°C.                                                                                                                                  | 155   |

| Figure 3-62: Maximum capacitor temperatures plotted versus the bus bar cold plate convective                                                                                                  |       |

| thermal resistance. The 175°C, 200°C, and 250°C junction temperature case results are                                                                                                         |       |

| provided. Results indicated that mounting cold plates to the bus bars enables capacitor                                                                                                       |       |

| temperature to operate below 85°C at all junction temperatures evaluated                                                                                                                      | 155   |

| Figure 3-63: Maximum capacitor temperatures plotted versus the bus bar cold plate convective                                                                                                  |       |

| thermal resistance for the 250°C junction temperature case. The effect of increasing the bus                                                                                                  |       |

| bar cooled surface area (increasing the bus bar cooled length to 30 mm, 60 mm, and 90                                                                                                         |       |

| mm, see Figure 3-59) on capacitor temperatures was evaluated. Cooling was only applied                                                                                                        |       |

| to one side of the bus bars. The figure legend provides the total cooled area                                                                                                                 |       |

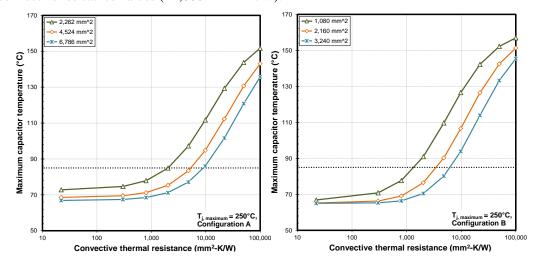

| Figure 3-64: SiC MOSFET Static Characterization.                                                                                                                                              |       |

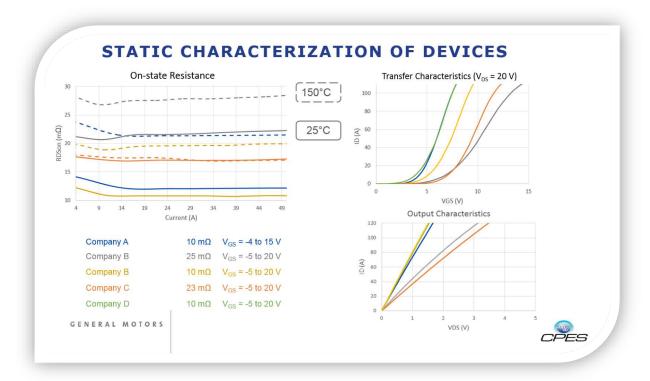

| Figure 3-65: SiC MOSFET Dynamic Characterization                                                                                                                                              |       |

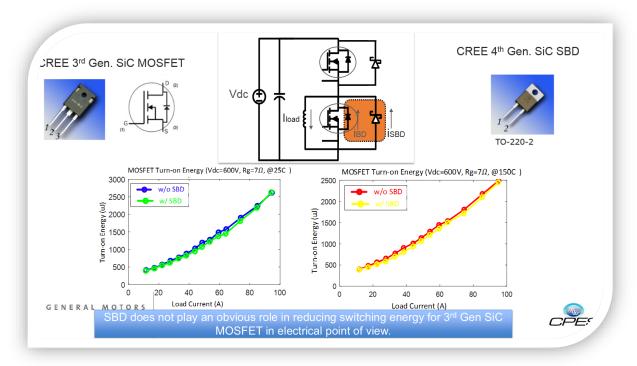

| Figure 3-66: MOSFET Turn-on and Turn-off Energy with and without SBD at 25°C & 150°C                                                                                                          | 162   |

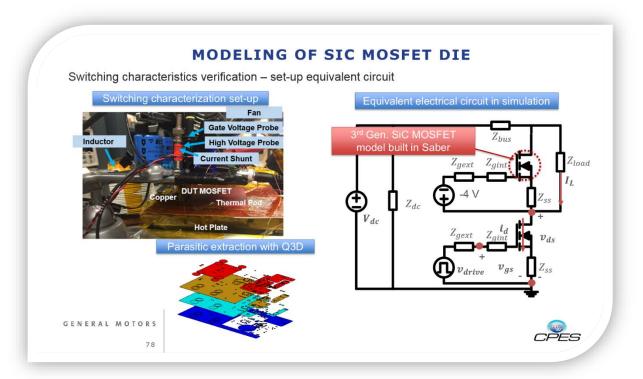

| Figure 3-67: SiC MOSFET Modeling                                                                                                                                                              |       |

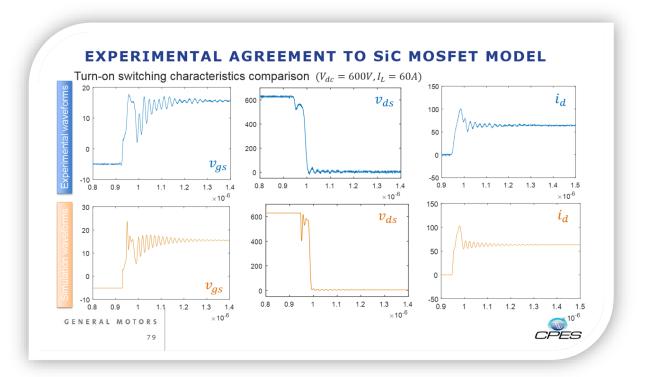

| Figure 3-68: Experimental Agreement to SiC MOSFET Model                                                                                                                                       |       |

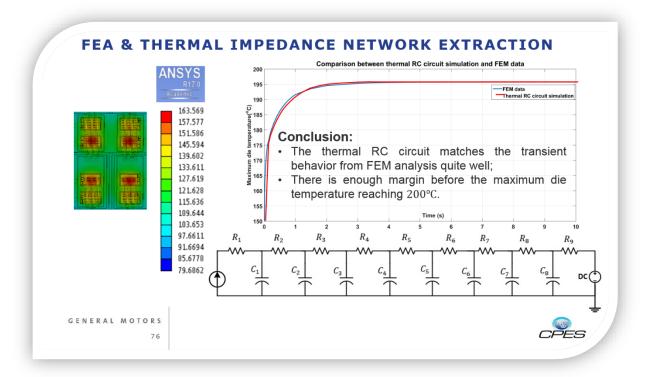

| Figure 3-69: Power Module Concept design - FEA & Thermal impedance network extraction                                                                                                         |       |

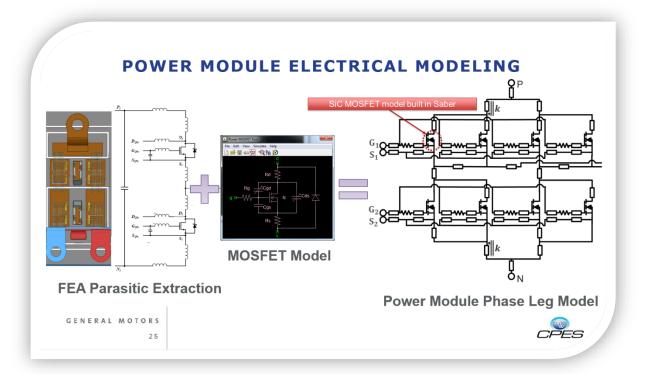

| Figure 3-70: Power Module Concept design - Electrical Modeling                                                                                                                                | 166   |

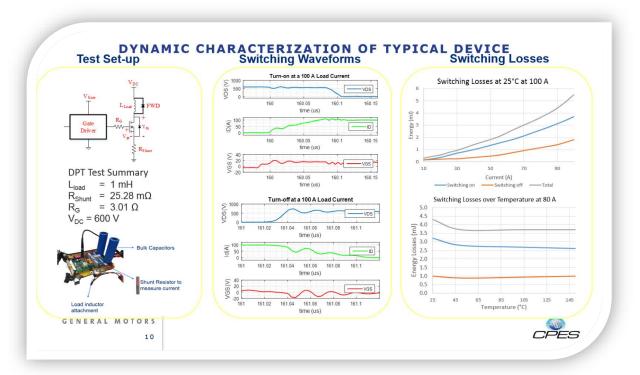

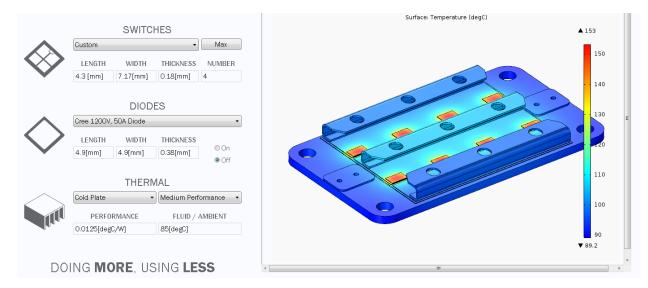

| Figure 3-71: This work brought together a team which is leading the market in SiC power device                                                                                                |       |

| production (Cree), SiC power module technology (Cree Fayetteville, formerly APEI), and                                                                                                        |       |

| HEV/EV platforms in the US market (Ford). Cree is the leading supplier of SiC and GaN                                                                                                         |       |

| components, including SiC power MOSFETs and diodes, and is also an automotive                                                                                                                 |       |

| supplier of SiC diodes to HEV / EV platforms. Cree-Fayetteville is a leading producer of                                                                                                      |       |

| high-temperature and low-inductance modules, which take full advantage of SiC power                                                                                                           |       |

| devices. Cree-Fayetteville has also constructed automotive drive train prototype inverters                                                                                                    |       |

| in concert with other automotive OEMs on other efforts. Ford is the number one US                                                                                                             | 1.00  |

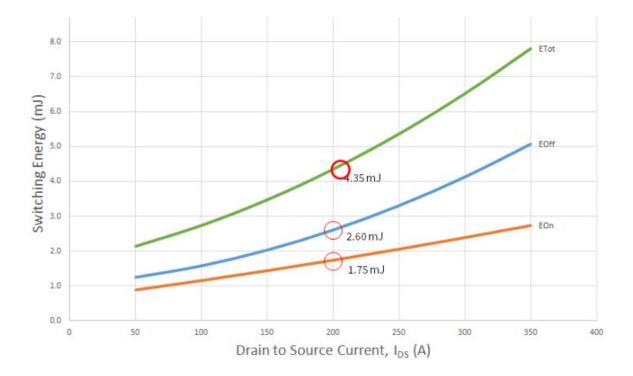

| producer of HEV / EV platforms, with a 13% market share in the US at the end of 2013<br>Figure 3-72: Comparison of measured switching energy for a 900V, 360A, 2.5 m $\Omega$ SiC half-bridge | 108   |

| power module over drain current, with respect to data sheet values of Si IGBT based power                                                                                                     |       |

| modules. Measuring at 600V, 200A, total switching energy was 4.35mJ. Switching energy                                                                                                         |       |

| of the SiC based module are 5-14 times lower than benchmark Si based modules                                                                                                                  | 171   |

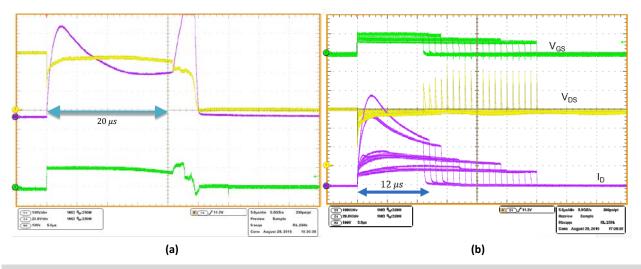

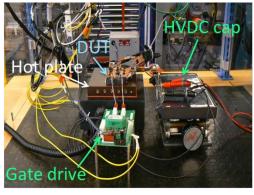

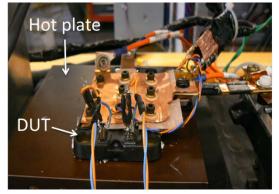

| Figure 3-73: Double pulse test setup to measure switching energies of a 900V, 360A, 2.5 m $\Omega$ SiC                                                                                        | 1 / 1 |

| half-bridge power module.                                                                                                                                                                     | 172   |

| Figure 3-74: Circuit used for measurement comparison of switching characteristics of the 900V, 10                                                                                             | 1 / 2 |

| $m\Omega$ SiC MOSFET in a TO-247-3L package and a TO-247-4L (source Kelvin contact)                                                                                                           |       |

| packagepackage wieds E1 in a 10-247-3D package and a 10-247-4D (source Retvin contact)                                                                                                        | 172   |

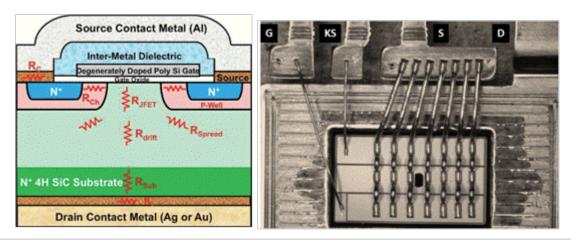

| Figure 3-75: 900V, $10\text{m}\Omega$ , $32\text{mm}2$ SiC MOSFET shown in top view (left) and cross-section (right).                                                                         | 1 / 2 |

| The top photo illustrates the three source pads, gate pad, and Kelvin source contacts. The                                                                                                    |       |

| cross-section illustrates the planar DMOS cross-section of the MOSFET device                                                                                                                  | 173   |

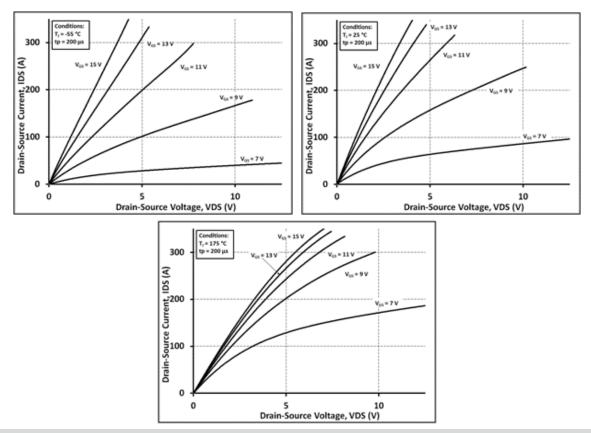

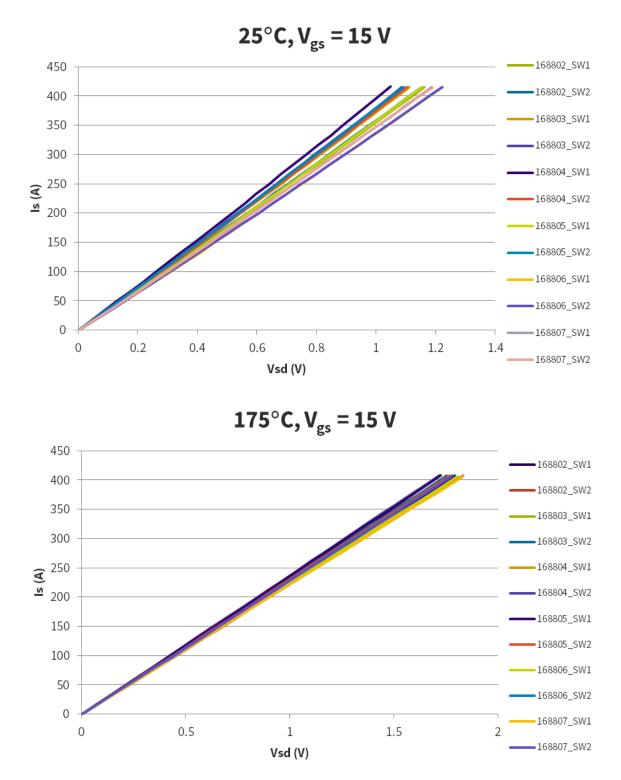

| Figure 3-76: DC output characteristics of 900V, 10mΩ SiC MOSFET at -55°C (top left), 25°C (top                                                                                                | 1 7 5 |

| right), and +175°C (bottom) temperature. The maximum DC operating point of the gate                                                                                                           |       |

| voltage is +15V, with a typical threshold voltage of 2.4V at 25°C                                                                                                                             | 174   |

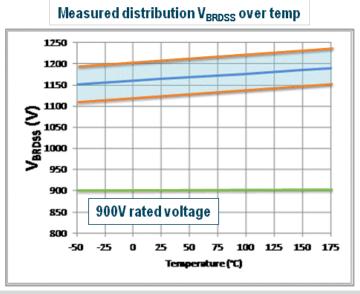

| Figure 3-77: Typical VBRDSS ranges from 1150V at -55°C to 1180V at 175°C of the 900V, $10\text{m}\Omega$                                                                                      |       |

| rated SiC MOSFET. Minimum VBRDSS of >1100V over all temperatures measured for                                                                                                                 |       |

| sample distribution of parts.                                                                                                                                                                 | 174   |

| Figure 3-78: Switching Energy losses at 25°C for the 900V for 900V, 10 m□ SiC MOSFET in TO-                                                                                                   |       |

| 247-4 package (RG=50hm, VGS=-4V/+15V, VDD=600V)                                                                                                                                               | 176   |

| Figure 3-79: 900 V SiC-optimized high-power inverter for three phase evaluation                                                                                                               |       |

| Figure 3-80: Four of eight die positions populated in the half-bridge power module with 900V, $10\text{m}\Omega$                                                                              |       |

| SiC MOSFETs. Upper image illustrates thermal simulation of all eight MOSFETs inside                                                                                                           |       |

| the power module, with peak temperature of 150°C on each die. Lower image illustrates a                                                                                                       |       |

| close-up of four MOSFETs in a single switch position inside the module                                                                                                                        | 177   |

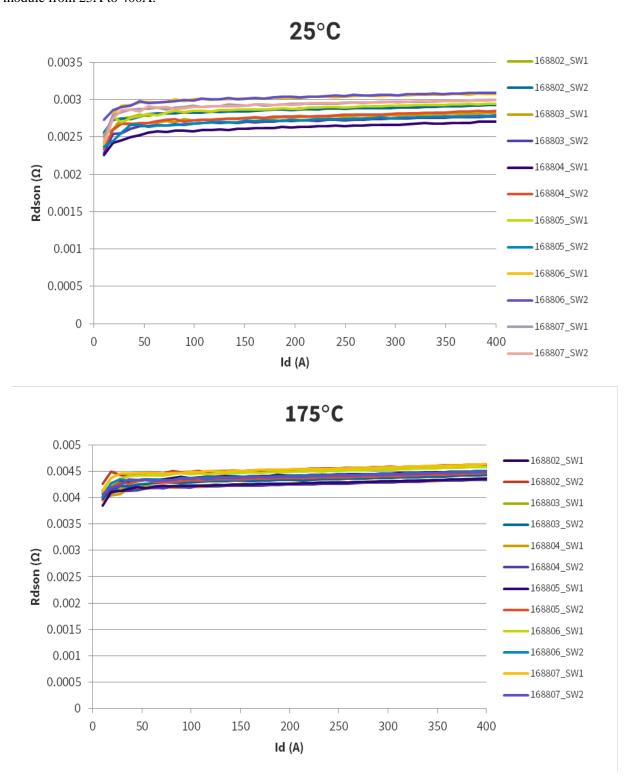

| Figure 3-81: 900V, $2.5m\Omega$ , half-bridge SiC power module on-state resistance as a function of drain-                                                                                    |       |

| source current up to 400A; (top) 25°C; (bottom) 175°C.                                                                                                                                        | 178   |

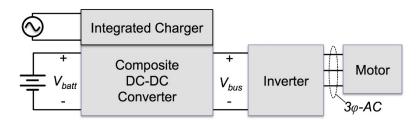

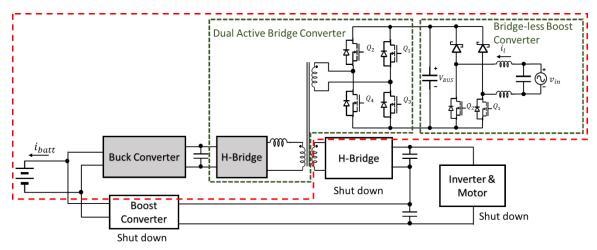

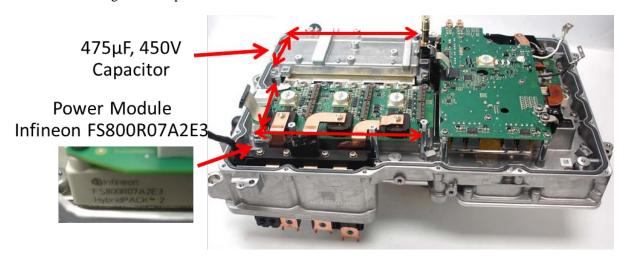

| Figure 3-82: Composite converter powertrain approach with integrated charger                                                                                                                  | 183   |

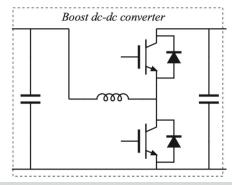

| Figure 3-83: Conventional boost converter power stage                                                                                                                                                                                                             | 183 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

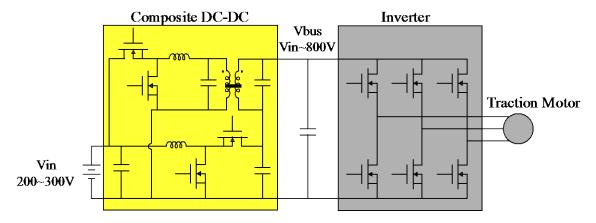

| Figure 3-84: Power electronics architecture for this project, including a DC-DC composite boost                                                                                                                                                                   |     |

| converter and an inverter.                                                                                                                                                                                                                                        | 184 |

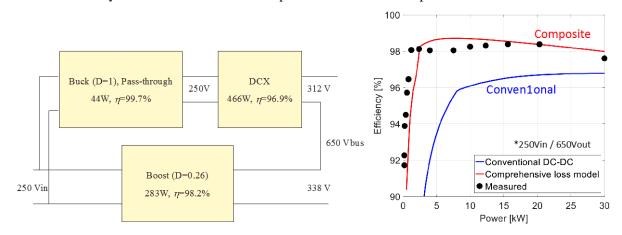

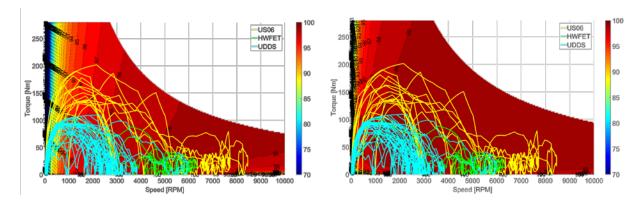

| Figure 3-85: Achieving high efficiency at high boost ratio in the composite architecture. Left: module operating points and losses at 250V: 650V, 30 kW. Right: comparison of efficiency curves                                                                   | 104 |

| of conventional boost converter with composite design, at 250V: 650V                                                                                                                                                                                              | 104 |

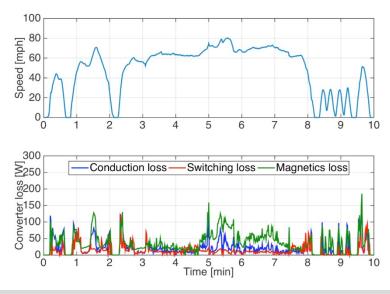

| converter. Top: US06 speed profile. Bottom: total semiconductor conduction loss,                                                                                                                                                                                  |     |

| switching loss, and dc+ac magnetics losses.                                                                                                                                                                                                                       | 195 |

| Figure 3-87: Photograph of assembled silicon prototype.                                                                                                                                                                                                           |     |

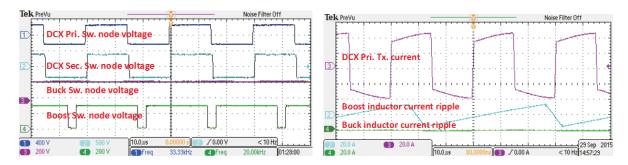

| Figure 3-87: Photograph of assembled shicon prototype.  Figure 3-88: Prototype measured waveforms, operating at 250 V battery voltage, 650 V dc bus                                                                                                               | 160 |

| voltage, and 50% of rated power (15 kW). Left oscilloscope figure waveforms, from top to bottom: DCX primary switch node voltage, DCX secondary switch node voltage, buck module switch node voltage, boost module switch node voltage. Right oscilloscope figure |     |

| waveforms, from top to bottom: DCX primary transformer current, boost inductor current,                                                                                                                                                                           |     |

| buck inductor current. At this operating point, the buck module operates in passthrough                                                                                                                                                                           |     |

| mode                                                                                                                                                                                                                                                              | 186 |

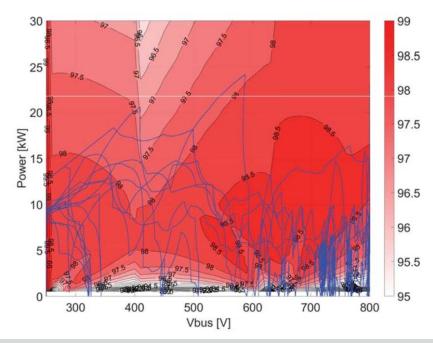

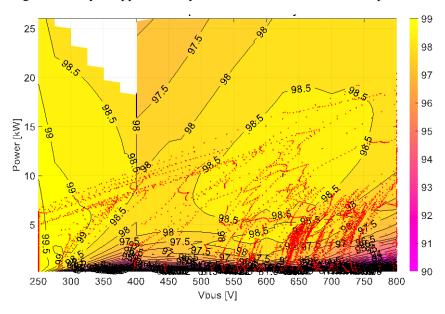

| Figure 3-89: Efficiency contours of the Si composite boost converter system, with superimposed                                                                                                                                                                    |     |

| US06 operating points.                                                                                                                                                                                                                                            | 187 |

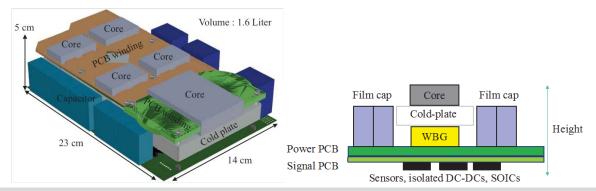

| Figure 3-90: High-density composite boost mechanical design. Left: CAD drawing of assembled unit.                                                                                                                                                                 |     |

| Right: Side view of mechanical layout. An off-the-shelf cold plate provides water cooling,                                                                                                                                                                        |     |

| with ferrite cores mounted on top side and wide bandgap semiconductors mounted on                                                                                                                                                                                 |     |

| bottom side. A PCB with high-weight copper provides power interconnects, and a PCB                                                                                                                                                                                |     |

| with conventional copper provides gate driver and signal interconnects                                                                                                                                                                                            | 188 |

| Figure 3-91: Assembled high-density composite boost converter laboratory prototype. Left: top side,                                                                                                                                                               |     |

| with planar magnetics visible. Right: bottom side, with signal PCB visible                                                                                                                                                                                        | 189 |

| Figure 3-92: Predicted efficiency contours of the SiC composite dc-dc converter system at Vbatt = 250                                                                                                                                                             |     |

| V and with 100°C junction temperature. The red dots represent superimposed operating                                                                                                                                                                              | 100 |

| points during the US06 drive cycle.                                                                                                                                                                                                                               | 189 |

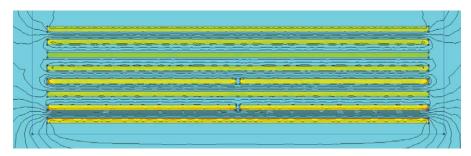

| Figure 3-93: Two-dimensional finite element modeling of the DCX planar transformer. The eight-                                                                                                                                                                    |     |

| layer PCB employs primary and secondary windings interleaved as follows: -1/1/-1/1/-2/1/-                                                                                                                                                                         | 101 |

| 2/1. Negative numbers denote secondary layers.                                                                                                                                                                                                                    | 191 |

| Figure 3-94: Two-dimensional finite element modeling of the boost module planar inductor. The six-                                                                                                                                                                | 101 |

| layer PCB employs six turns, with one turn per layer and 5 oz copper                                                                                                                                                                                              | 191 |

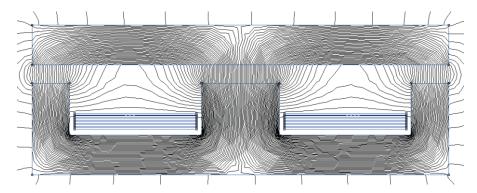

| 600 V Si IGBT inverter. Right: 1200 V SiC MOSFET inverter                                                                                                                                                                                                         | 101 |

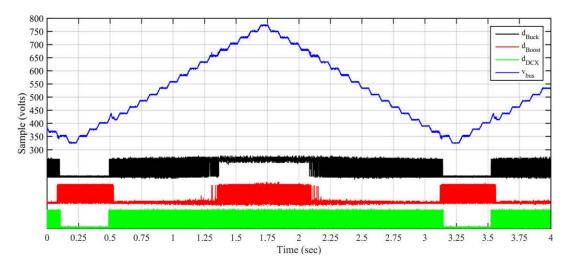

| Figure 3-96: Simulink model of controller algorithms for composite boost system with 250 V battery                                                                                                                                                                | 191 |

| input. The commanded bus voltage is stepped from 300 V to 800 V and back. The system automatically switches modes as necessary, and the transient response is well behaved                                                                                        | 102 |

| Figure 3-97: Integrating an on-board charger into the composite boost architecture. Add additional                                                                                                                                                                | 192 |

| output is added to the DCX (DAB) and a bridgeless boost converter is added for power                                                                                                                                                                              |     |

| factor correction.                                                                                                                                                                                                                                                | 193 |

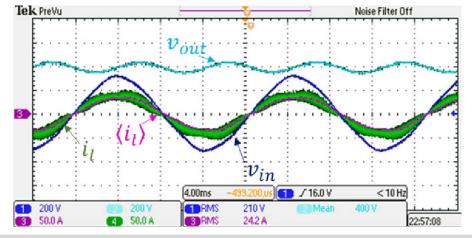

| Figure 3-98: Measured waveforms of power factor correction module (bridgeless boost) prototype: ac                                                                                                                                                                | 175 |

| line voltage (purple), inductor current (green), and dc output voltage (blue), operating at                                                                                                                                                                       |     |

| 210 Vrms input, 400 Vdc output, and 5 kW power                                                                                                                                                                                                                    | 193 |

| Figure 4-1: 2016 BMW i3 inverter assembly: (a) isometric view and (b) side view                                                                                                                                                                                   |     |

| Figure 4-2: 2016 BMW i3 inverter assembly with top cover removed: (a) front and (b) side                                                                                                                                                                          |     |

| Figure 4-3: Location of inverter components in 2016 BMW i3 inverter assembly.                                                                                                                                                                                     |     |

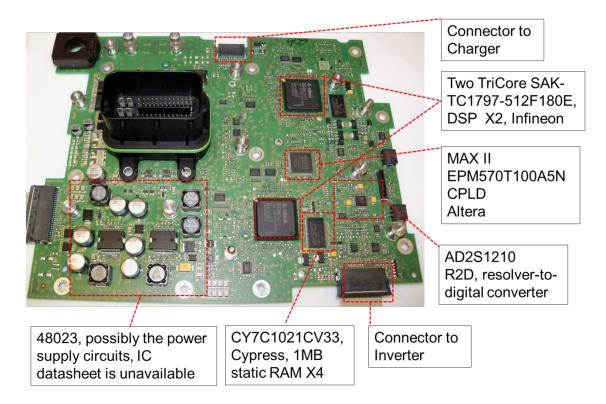

| Figure 4-4: Key components on control board in 2016 BMW i3 inverter assembly                                                                                                                                                                                      |     |

| Figure 4-5: Key components on driver board in 2016 BMW i3 inverter power module                                                                                                                                                                                   |     |

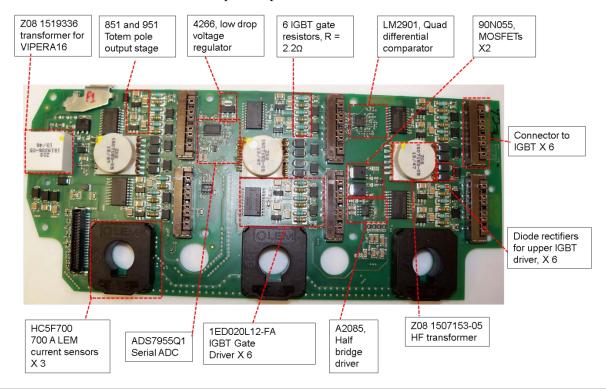

| Figure 4-6: 2016 BMW i3 Infineon three-phase inverter power module with cover removed                                                                                                                                                                             |     |

| Figure 4-7: IGBTs and diodes in 2016 BMW i3 Infineon inverter power module                                                                                                                                                                                        |     |

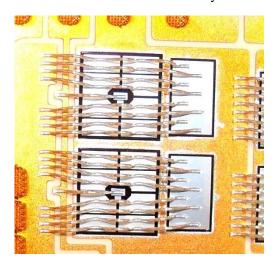

| Figure 4-8: 2016 BMW i3 motor assembly (a) and motor assembly with outer case removed (b)                                                                                                                                                                         |     |

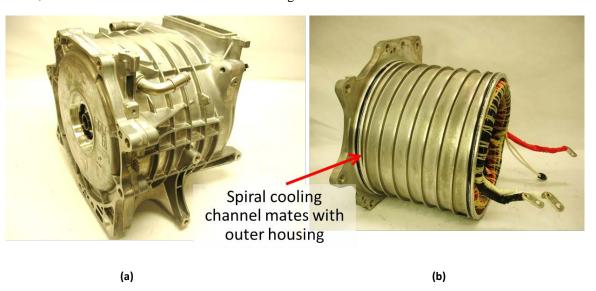

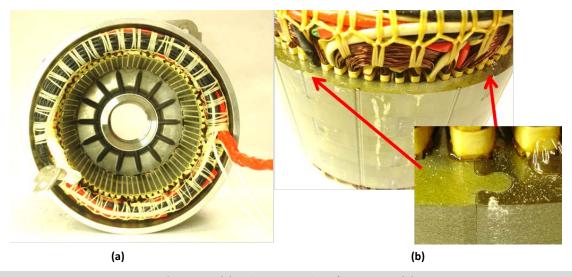

| Figure 4-9: 2016 BMW i3 motor stator front view (a) and stator windings/laminations (b)                                                                                                                                                                           |     |

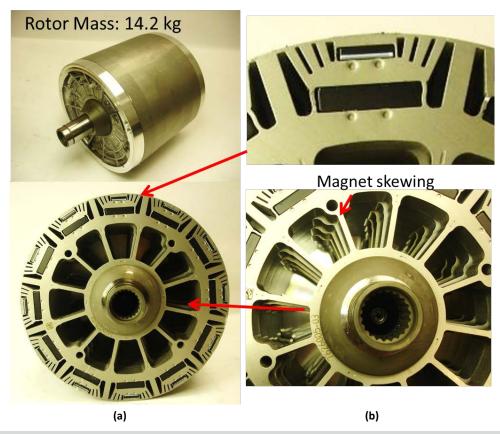

| Figure 4-10: 2016 BMW i3 motor rotor (a) and rotor magnets (b)                                                                                                                                                                                                    |     |

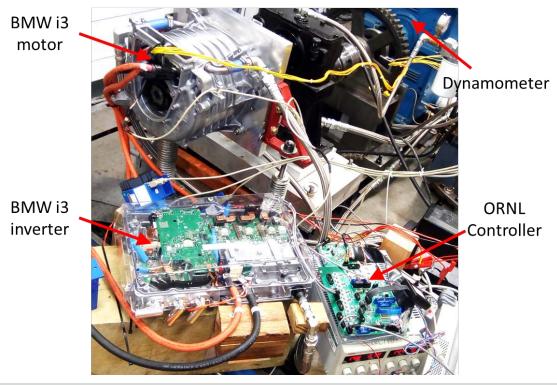

| Figure 4-11: 2016 BMW i3 motor and inverter installed in ORNL dynamometer test cell                                                                                                                                                                               |     |

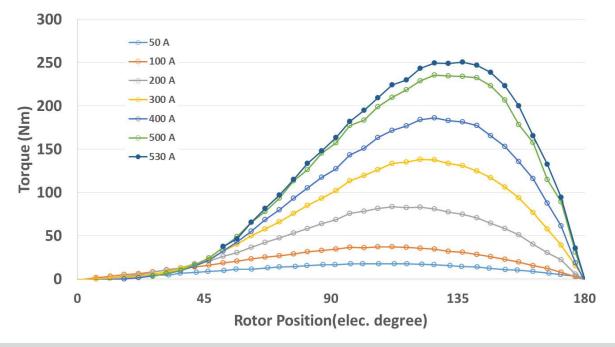

| Figure 4-12: 2016 BMW i3 motor locked rotor torque versus position for various dc levels                                                                                                                                                                          |     |

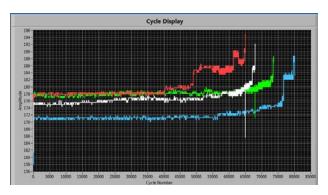

| Figure 4-13: 2016 BMW i3 motor peak locked rotor torque versus position                                |     |

|--------------------------------------------------------------------------------------------------------|-----|

| Figure 4-14: 2016 BMW i3 motor efficiency map.                                                         |     |

| Figure 4-15: 2016 BMW i3 inverter efficiency map.                                                      |     |

| Figure 4-16: 2016 BMW i3 motor/inverter combined efficiency map.                                       | 205 |

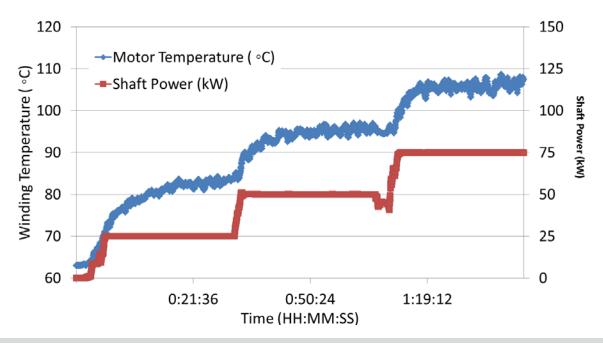

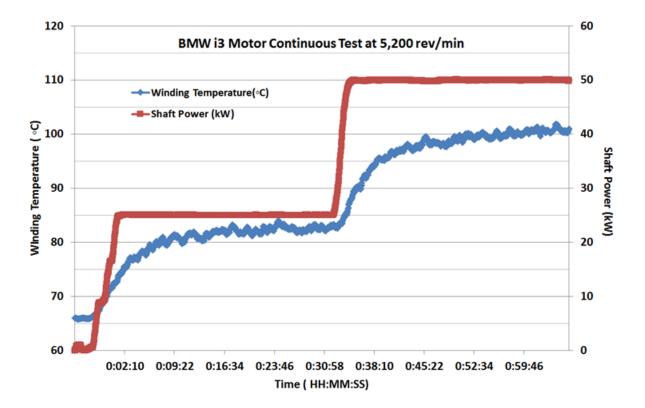

| Figure 4-17: Continuous tests of 2016 BMW i3 motor and inverter at 7,000 rpm and various power         |     |

| levels.                                                                                                | 205 |

| Figure 4-18: Continuous tests of 2016 BMW i3 motor and inverter at 5,000 rpm and various power         |     |

| levels.                                                                                                | 206 |

| Figure 4-19: Pictures of the 2014 Honda Accord inverter. The left image shows the entire power         |     |

| electronics system and the middle image presents the cold plate cooling channels. The                  |     |

| image on the right shows the intricate fins directly fabricated on the cold plate                      | 210 |

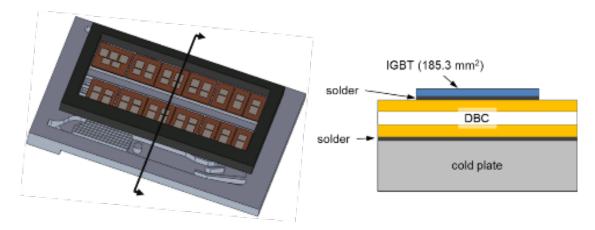

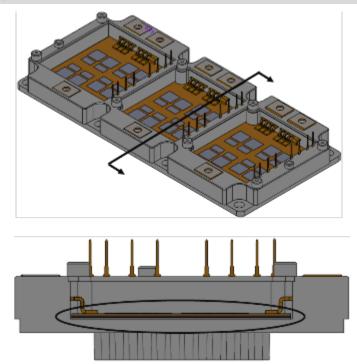

| Figure 4-20: CAD model of the Honda Accord power module (left). The various power module layers        |     |

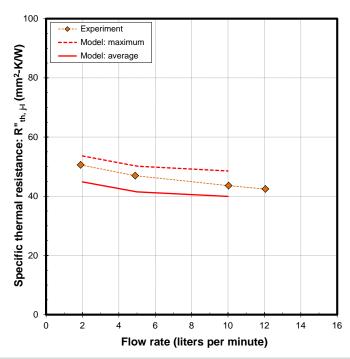

| are shown in the cross-section view on the right                                                       | 210 |

| Figure 4-21: Experimentally measured and model-predicted IGBT thermal resistance values for the        |     |

| 2014 Honda Accord inverter.                                                                            | 211 |

| Figure 4-22: CFD-generated plot showing the liquid velocity streamlines at a flow rate of 10 Lpm (left |     |

| iamge) and the temperature distribution (right image) on the cold plate surface                        | 212 |

| Figure 4-23: Temperature profile through the Accord inverter depicting the thermal path from the       |     |

| IGBT to the liquid. The silicon nitride layer constitutes a significant thermal resistance in          |     |

| the power modules.                                                                                     | 213 |

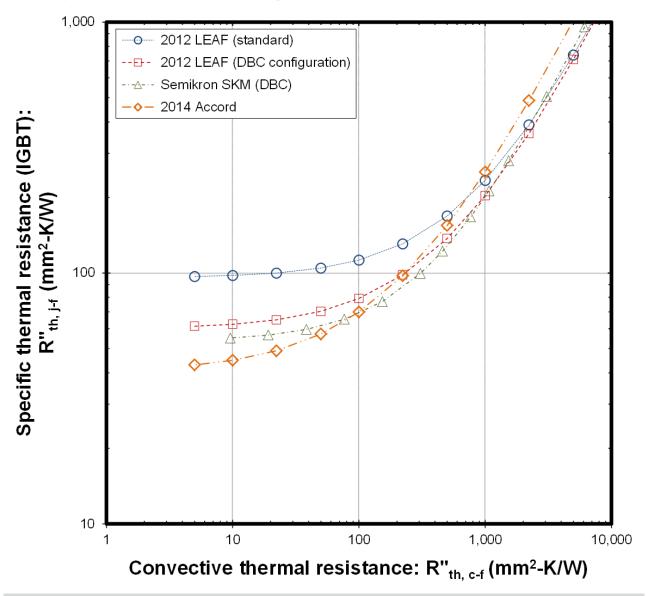

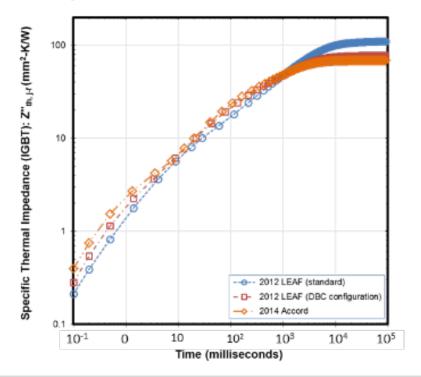

| Figure 4-24: Specific (junction-to-liquid) thermal resistance versus the convective thermal resistance |     |

| for the standard LEAF, DBC-modified LEAF, the Accord, and Semikron modules. The                        |     |

| Semikron data were from Bennion and Moreno [8]                                                         | 214 |

| Figure 4-25: Transient junction-to-liquid thermal impedance plotted versus time                        | 215 |

| Figure 4-26: Pictures of the 2015 BMW i3 inverter. The left image is the top view of the i3 EME        |     |

| system. The middle image shows the cold plate cooling channels. The image on the right                 |     |

| shows the power block mounted on the cold plate                                                        | 216 |

| Figure 4-27: CAD model of the BMW i3 power module (top). The various power module layers are           |     |

| circled out in the lower cross-section view.                                                           | 216 |

| Figure 4-28: Specific (junction-to-liquid) thermal resistance plotted versus the convective thermal    |     |

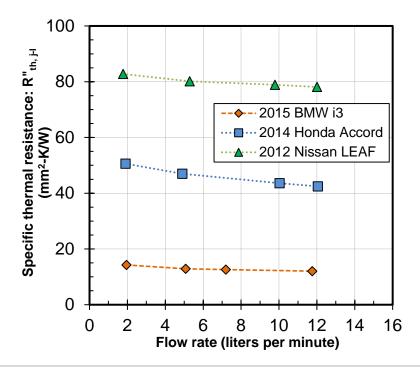

| resistance for the 2012 LEAF, 2014 Accord and 2015 BMW i3 power electronics systems                    | 217 |

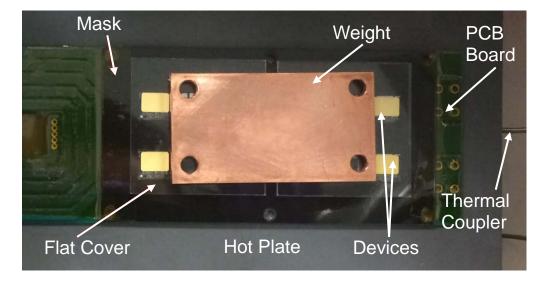

| Figure 5-1: Photo of the final assembly of all parts for soldering multiple GaN MOSFETS (devices)      |     |

| on a PCB board on a hot plate in a solder reflow oven to form a power module                           | 222 |

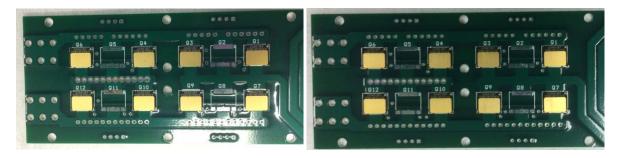

| Figure 5-2: Two packaged GaN MOSFET power phase legs (eight MOSFETS each) for assembly of a            |     |

| GaN charger converter (project EDT 054)                                                                | 222 |

| Figure 5-3: Analysis of parasitic inductance in the 2013 Toyota Camry inverter: (a) planar power       |     |

| modules with overlaid electric diagrams, (b) photo of partial inverter with copper                     |     |

| terminals, (c) 3-D model of the electrical interconnection in inverter module, and (d)                 |     |

| lumped element model of parasitic electric components with illustrated major power                     |     |

| commutation loops                                                                                      | 223 |

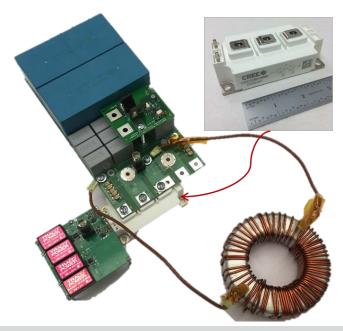

| Figure 5-4: The test setup for evaluation of switching performance of a SiC module: CREE's             |     |

| CAS120M12BM2 (upper right corner)                                                                      | 224 |

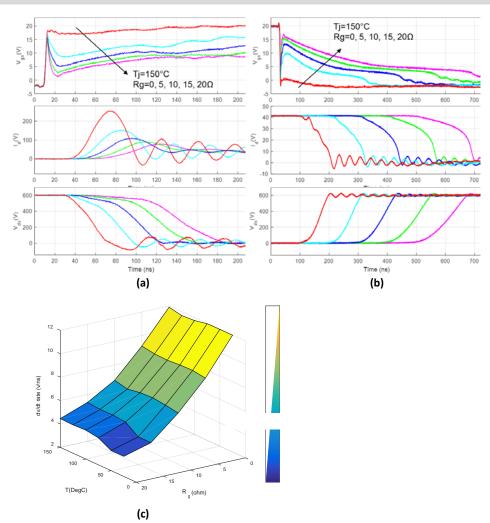

| Figure 5-5: Measured switching performance of Cree SiC MOSFET in module CAS120M12BM2:                  |     |

| waveforms of the current Id, voltages Vds, Vgs at $Tj = 150^{\circ}C$ with the gate resistance         |     |

| varying from 0 to 20 $\Omega$ [(a) and (b)]; dV/dt dependences on both Rg and operation                |     |

| temperature (c).                                                                                       | 224 |

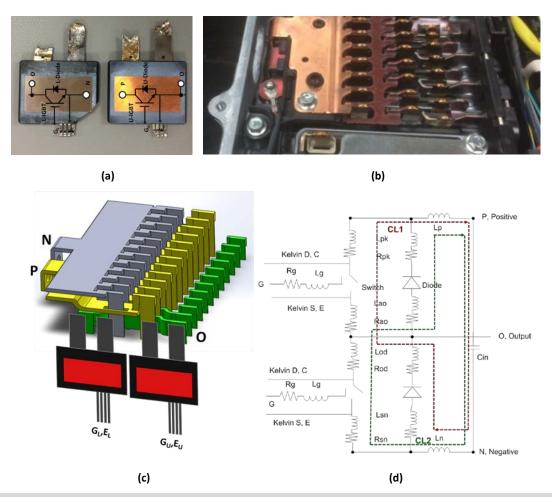

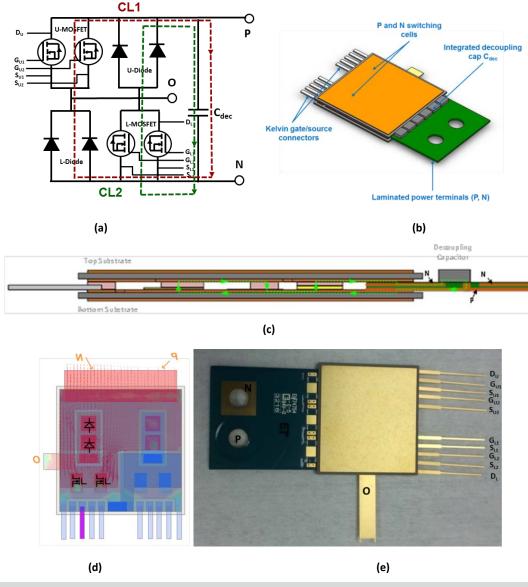

| Figure 5-6: Design of an ultralow inductance SiC phase-leg module: (a) electric diagram with           |     |

| regrouped switches; (b) aerial view of the planar package; (c) cross-sectional view of the             |     |

| interconnections and current in commutation loop; (d) current density distribution in the              |     |

| package along a commutation loop; and (e) photo of laminated planar-bond-all package of                |     |

| a 100 A, 1,200 V SiC MOSFET/JBS diode phase-leg power module                                           | 225 |

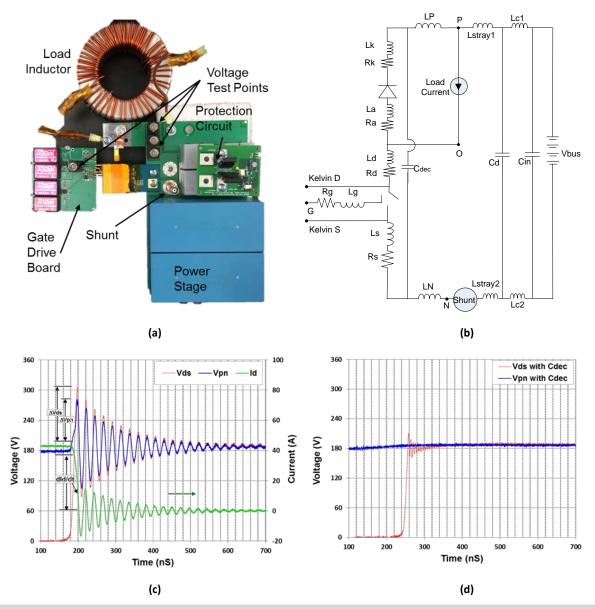

| Figure 5-7: Test of the electrical performance of packaged modules: (a) experiment setup; (b) electric |     |

| diagram of the test circuit (c) typical waveforms of switch turning off; and (d) waveforms             |     |

| with added decoupling caps.                                                                            | 227 |

| Figure 5-8: Planar bond of SiC dies in package: (a) Cross-sectional view of a SiC die bonded onto a    |     |

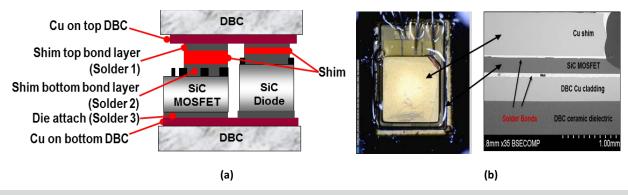

| DBC substrate through shims; (b) photos of a shim bonded on SiC MOSFET                                 | 228 |

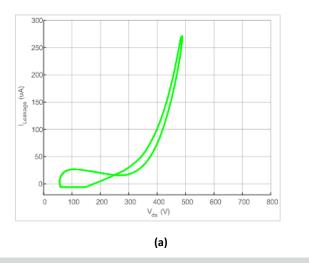

| Figure 5-9: Leakage current of SiC MOSFET in different packages: (a) AuSn soldered copper shim;          |     |

|----------------------------------------------------------------------------------------------------------|-----|

| (b) wire-bonded package and PbSnAg soldered shim                                                         | 228 |

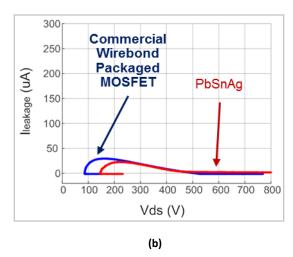

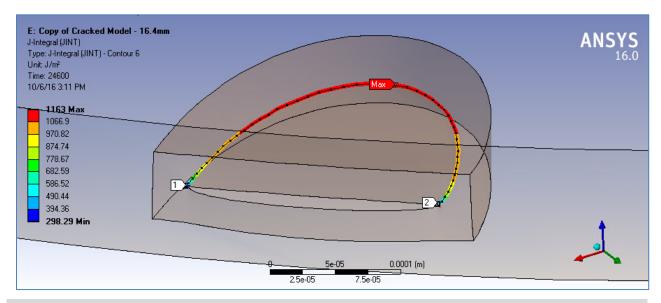

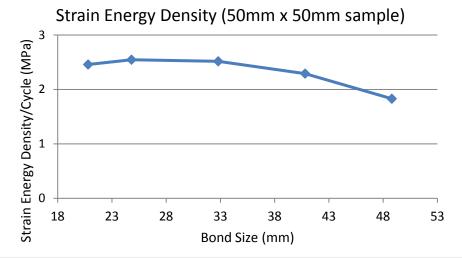

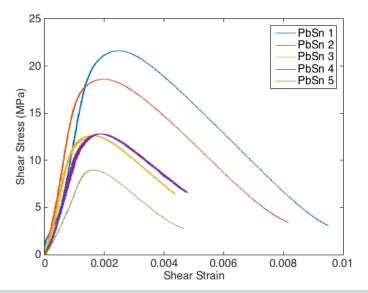

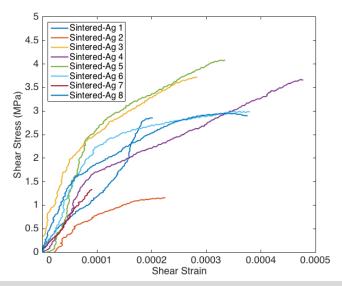

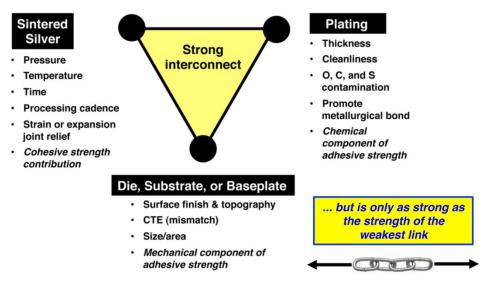

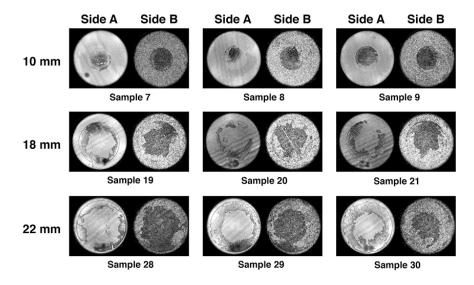

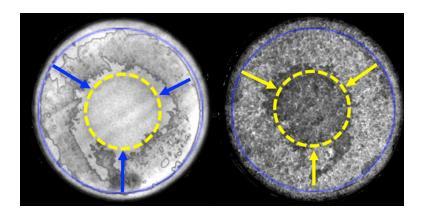

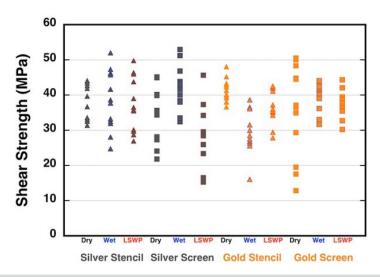

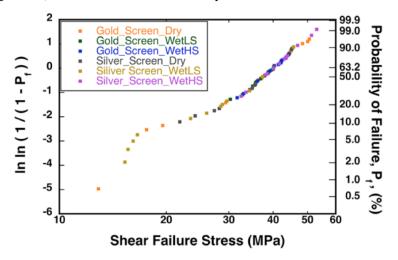

| Figure 5-10: Experimental studies of silver sintered die bonds: (a) cross-sectional view of sintered     |     |

| silver bond of SiC die on DBS, (b) broken interface of bonded die on DBC, (c) three bond                 |     |

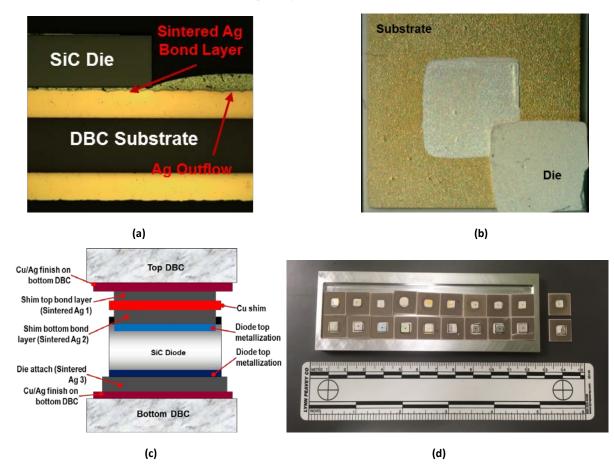

| layers in planar package, and (d) photo of sheared off samples                                           | 229 |

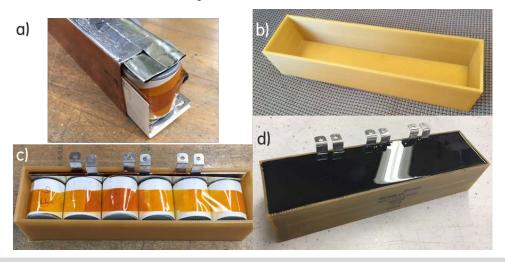

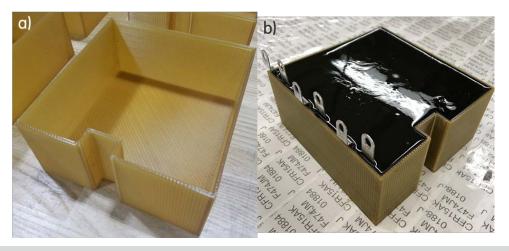

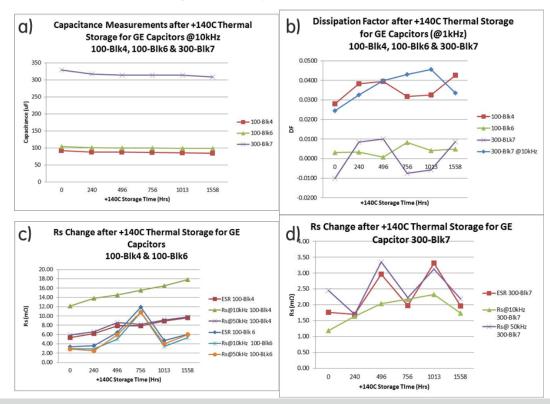

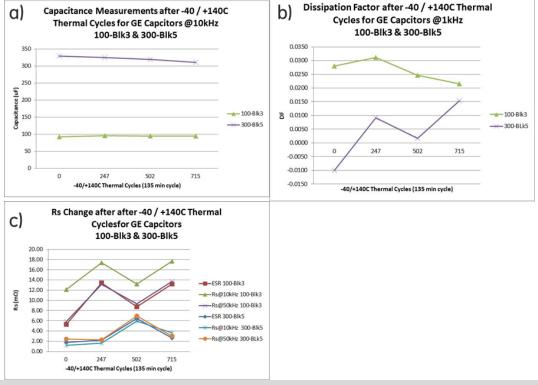

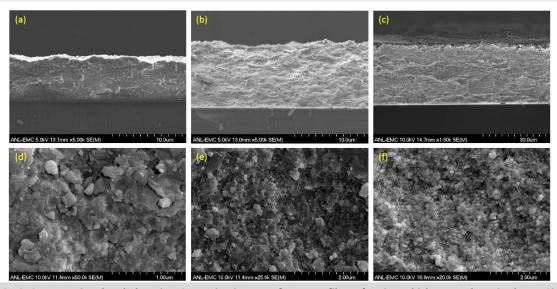

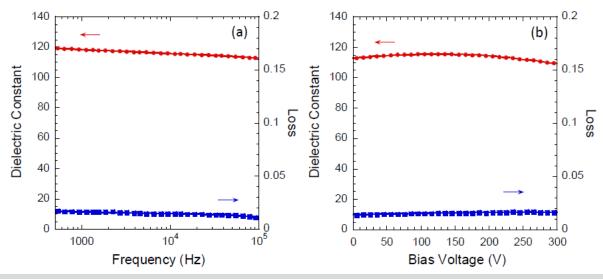

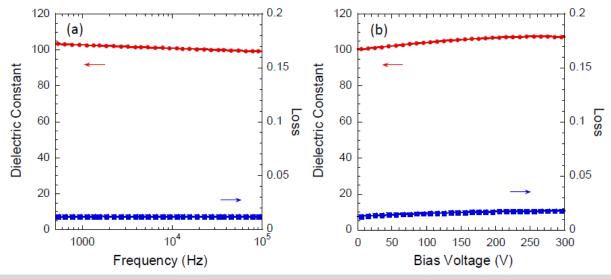

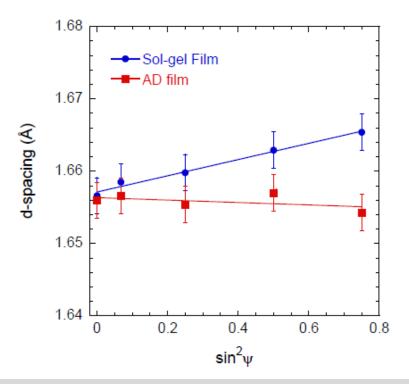

| Figure 5-11: Shear strength of three bond layers.                                                        | 230 |