# 650V SiC Integrated Power Module for Automotive Inverters

### Monty B. Hayes

Delphi Automotive Systems, LLC

Project Number: EDT083

This presentation does not contain any proprietary, confidential, or otherwise restricted information.

06/07/2017

# **Project Overview**

### Timeline

Project Start Date: January 1, 2016 Project End Date: February 28, 2018 Percent Complete: 40%

### **Barriers**

| Cost (\$/kW)           | <3.3  |

|------------------------|-------|

| Specific Power (kW/kg) | >14.1 |

| Power Density (kW/L)   | >13.4 |

| Budget                               | Partners                   |                            |

|--------------------------------------|----------------------------|----------------------------|

| Total Project Funding:<br>DOE Share: | \$2,161,561<br>\$1,488,303 | Delphi - Lead<br>Wolfspeed |

| Contractor Share:                    | \$673,258                  | Oak Ridge National Labs    |

| Funding Received in 2016             | : \$656,921                | Volvo                      |

| Funding for FY 2017:                 | \$831,381                  |                            |

## **Relevance Project Objectives**

- Develop a double-sided cooled 650V Silicon Carbide (SiC) Metal Oxide Semiconductor Field Effect Transistor (MOSFET) packaged power device

- Capable of traction drive inverter application targeted to meet DOE's 2020 electric drive vehicle (EDV) inverter targets as shown

| Parameter              | Target |

|------------------------|--------|

| Cost (\$/kW)           | < 3.3  |

| Specific Power (kW/kg) | > 14.1 |

| Power Density (kW/L)   | > 13.4 |

### **Double-side cooled 650V SiC MOSFET Packaged Power Device**

### **Milestones**

- Optimization of SiC MOSFET with top-side metallurgy

- Semiconductor package design/layout turn 1

- SiC MOSFET power semiconductor device fabrication and characterization

- Semiconductor package characterization

- Prototype inverter performance

## **Milestones**

### Budget Period 1

| Milestone                                                | Туре      | Description                                                                                                                                                                                                                                                                                                                                                         | Status   |

|----------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Configuration<br>Selection                               | Technical | Selection of 650V SiC<br>MOSFET power<br>semiconductor<br>device/module with an<br>Rdson of 7-8 m $\Omega$ . The<br>down selection will include<br>device rated breakdown<br>voltage, current rating and<br>switching frequency for the<br>inverter application.                                                                                                    | Complete |

| Fabrication<br>Completed                                 | Technical | In Progress                                                                                                                                                                                                                                                                                                                                                         |          |

| Device Build<br>Completed                                | Technical | In Progress                                                                                                                                                                                                                                                                                                                                                         |          |

| Traction Drive<br>Inverter System<br>Design<br>Completed | Technical | Complete design of<br>Traction Drive Inverter<br>System                                                                                                                                                                                                                                                                                                             | Complete |

| Characterization<br>Completed                            | Go/No-Go  | SiC MOSFET packaged<br>devices characterized<br>across temperature and<br>design of inverter. Provide<br>characterization data for<br>the 7-8 m $\Omega$ device and<br>projected inverter<br>performance comparison to<br>the DOE 2020 goals. The<br>potential to meet cost and<br>performance goals are<br>assessed to determine if<br>the project should proceed. | Complete |

### Budget Period 2

| Milestone                                              | Туре                                  | Description                                                                 |             |  |  |

|--------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------|-------------|--|--|

| Characterization and<br>Pre-Qualification<br>Completed | Technical                             | Characterization<br>of SiC MOSFET<br>device completed                       | In Progress |  |  |

| Prototype Design<br>Completed                          | Technical                             | Prototype inverter<br>design/layout<br>completed                            | In Progress |  |  |

| Traction Inverter<br>Build and Evaluation<br>Completed | d Evaluation Technical traction drive |                                                                             |             |  |  |

| Prototype Test<br>Completed                            | Technical                             | Prototype inverter<br>hardware build,<br>debug and test<br>completed        | Not Started |  |  |

| Characterization<br>Completed                          | Technical                             | Semiconductor<br>package<br>characterization<br>and evaluation<br>completed | Not Started |  |  |

# Approach

| rogran    | n Development Schedule<br>Budget Period                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                           |                            |                  |     | Duda                   | ot F | Porio | A 14       |       |      |                                 |                  |    | <b>D</b> . | .da | ot D | orio  | 4.0 |    |    |       | _    |    |    |    |      | _    | _   | _ |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|----------------------------|------------------|-----|------------------------|------|-------|------------|-------|------|---------------------------------|------------------|----|------------|-----|------|-------|-----|----|----|-------|------|----|----|----|------|------|-----|---|

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                           |                            |                  |     |                        |      | Perio | <b>a</b> 1 |       | 1    |                                 |                  |    |            |     | et P | erio  | a 2 |    |    |       |      |    |    | 40 |      |      |     | _ |

|           | Years                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pre-A    |                           |                            |                  |     | <b>20</b> <sup>4</sup> | _    |       | -          |       |      |                                 |                  |    | 201        | _   | _    |       |     |    |    |       | -    |    | 20 | _  |      | _    | _   | 4 |

|           | Months                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -6 -5 -4 | -3 -2 -                   | 1                          | 23               | 4 5 | 6                      | 7    | 8 9   | 10         | 11 12 | ! 13 | 14 1                            | 15 16            | 17 | 18         | 19  | 20 2 | 21 22 | 23  | 24 | 25 | 26 27 | 7 28 | 29 | 30 | 31 | 32 3 | 3 34 | 4 3 | 5 |

|           | Customer Key Dates (TBD)                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                           | TDP Pr<br>(1)              | gm Appr.<br>1/15 |     |                        |      |       |            |       |      | DP Prgm<br>(2/1/17              |                  |    |            |     |      |       |     |    |    |       |      |    |    |    |      | _    |     |   |

|           | Delphi Key Development Dates/internal MRD<br>Design Reviews<br>Gate Reviews                                                                                                                                                                                                                                                                                                                                                                                             | Subm     | oosal<br>ission.<br>1015) | Design I<br>off<br>(12/1/1 | 5)               |     |                        |      |       |            |       |      | Design K<br>off<br>(1/1/17<br>• | iick<br>')<br>RR |    |            |     |      |       |     |    |    |       |      |    |    |    |      |      |     |   |

| TDP       | Analyze/Develop System Level OEM Spec<br>Investigate Topology with Semiconductor Device Supplier<br>Cree Task 1:<br>Optimization of 650V, 8mOhm SiC MOSFET with Top-Side<br>Metallurgy Soldering/Sintering Compatible<br>Development Lot 1 ECD<br>Development Lot 2 ECD<br>Development Lot 3 ECD<br>Package Design/Layout Turn 1<br>Part Sourcing & Procurement(14 weeks)<br>Build of Packaged Parts<br>Semiconductor Package Characterization and Pre-qual<br>Go/No Go |          |                           |                            |                  |     |                        |      | ◆     |            |       |      | •                               | •                |    | •          |     |      |       |     |    |    |       |      |    |    |    |      |      |     |   |

|           | Package Design/Layout Turn 2<br>Design/Layout<br>Part Sourcing & Procurement(14 weeks)<br>Build of Packaged Parts<br>Semiconductor Package Characterization and Pre-Qual<br>Go/No Go                                                                                                                                                                                                                                                                                    |          |                           |                            |                  |     |                        |      |       |            |       |      |                                 |                  |    |            |     |      |       |     |    |    |       |      |    |    |    |      |      |     |   |

| otype - D | Inverter Design/Layout<br>Part Sourcing and Procurement<br>Inverter Build<br>Inverter Evaluation and Testing                                                                                                                                                                                                                                                                                                                                                            |          |                           |                            |                  |     |                        |      |       |            |       |      |                                 |                  |    |            |     |      |       |     |    |    |       |      |    |    |    |      |      |     |   |

| Months    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | JAS      | 0 N [                     | J                          | FМ               | A M | IJ                     | J    | A S   | 0          | N D   | J    | FI                              | M A              | м  | J          | J   | A    | s o   | N   | D  | J  | FM    | A    | м  | J  | J  | A :  | s c  | 1 ( | N |

|           | Years                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20       | 15                        |                            |                  | :   | 20'                    | 16   |       |            |       | 1    |                                 |                  |    | 201        | 4 7 |      |       |     | :  | İ  |       | :    |    | 20 | 40 |      | _    |     | 7 |

### Technical Accomplishments Layout of Wolfspeed 650V SiC MOSFET

- Wolfspeed 650V G3 MOSFETs on a 4" wafer

- Die size 37mm<sup>2</sup>

- 1<sup>st</sup> Development lot received

- Mean Rdson ~7.7mΩ (at 75A, 25°C)

- Mean avalanche voltage 964V (25°C)

- V<sub>th</sub> > 2V

- Top-side metallization for Delphi packaging

- 500 samples shipped

| G      |   |

|--------|---|

|        |   |

|        |   |

| S      | S |

|        |   |

|        |   |

| See.   |   |

| 100.00 |   |

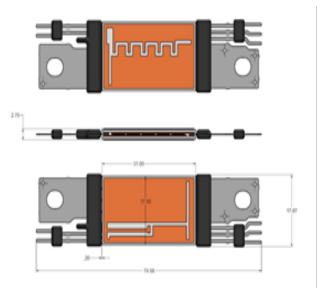

### Technical Accomplishments Dual-sided Cooled Packaged Device Assembly

- Delphi packaged power device

- 5 MOSFETs in parallel

- Thermistor

- Pb-free solder

- Build 1

- 90+% package electrical yield

- 50 packaged parts

- 250 Lot1 MOSFETs

### SiC Package Designed for 500Arms Capability

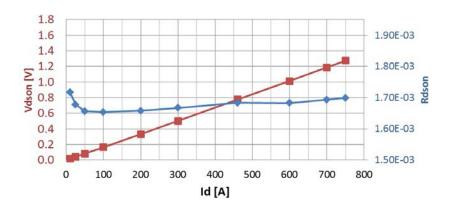

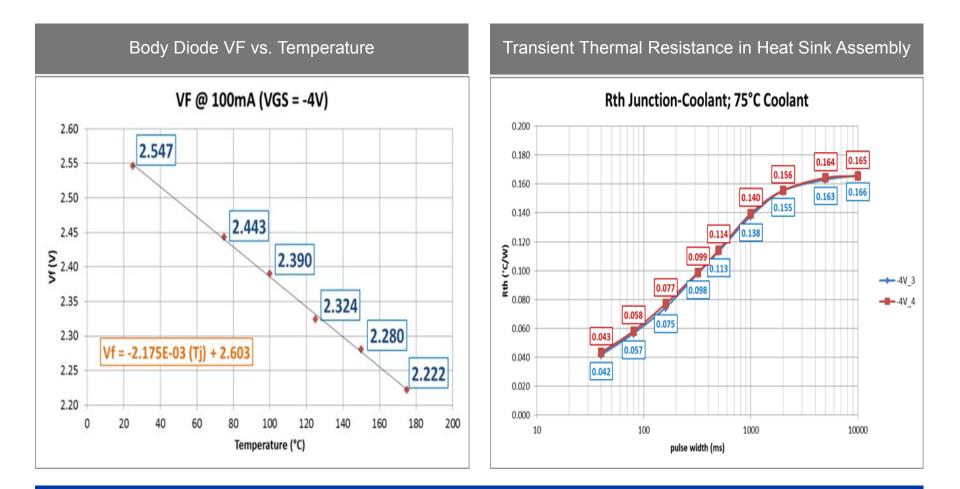

### Technical Accomplishments Static Characterization Packaged Semiconductor

#### 25°C DC characterization data

|               | Mean  | Std. Dev. |       |

|---------------|-------|-----------|-------|

| IGSS +20V     | 26.3  | 43.5      | рА    |

| Vf (100mA-4V) | 2.539 | 0.001     | V     |

| VT 200mA      | 2.088 | 0.116     | V     |

| IDSS 700V     | 3.69  | 1.69      | uA    |

| BVDSS 10mA    | 978.8 | 16.0      | V     |

| VDSON 750A    | 1.274 | 0.034     | V     |

| RON750        | 1.699 | 0.045     | mOhms |

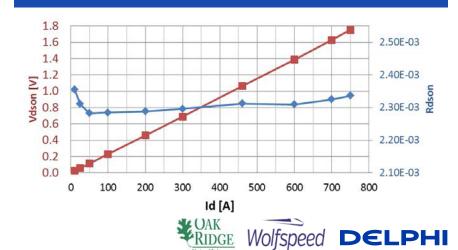

#### 175°C DC characterization data

| 12            |       |           |       |

|---------------|-------|-----------|-------|

|               | Mean  | Std. Dev. |       |

| IGSS +20V     | 360.7 | 99.8      | nA    |

| Vf (100mA-4V) | 2.203 | 0.006     | ٧     |

| VT 200mA      | 1.480 | 0.095     | V     |

| IDSS 700V     | 29.91 | 7.18      | uA    |

| BVDSS 10mA    | 986.6 | 15.1      | V     |

| VDSON 750A    | 1.752 | 0.036     | V     |

| RON750        | 2.336 | 0.048     | mOhms |

#### 25°C Package VDSON, RDSON

#### 175°C Package VDSON, RDSON

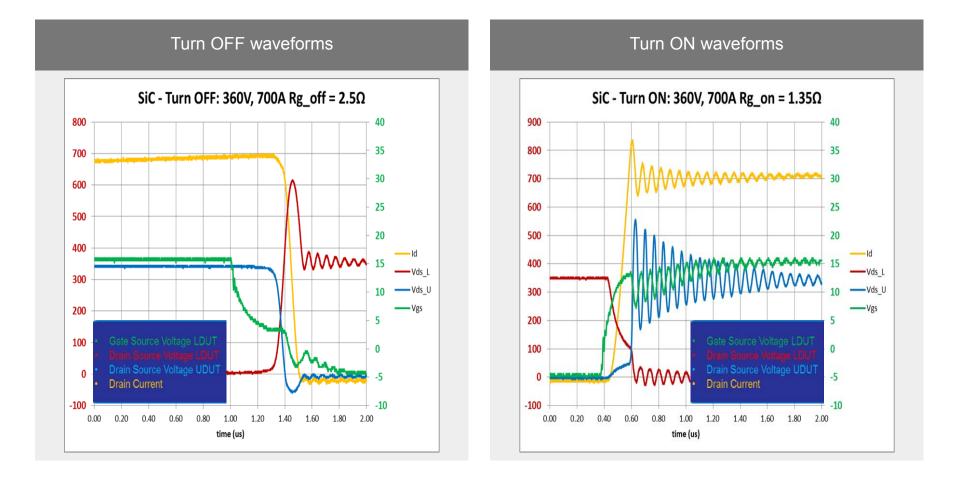

### Technical Accomplishments Dynamic Characterization Packaged Semiconductor

### **Packaged SiC MOSFET: Switching Waveforms**

### Technical Accomplishments Thermal Characterization of Heat Sink Assembly

Thermal characterization of heat sink assembly

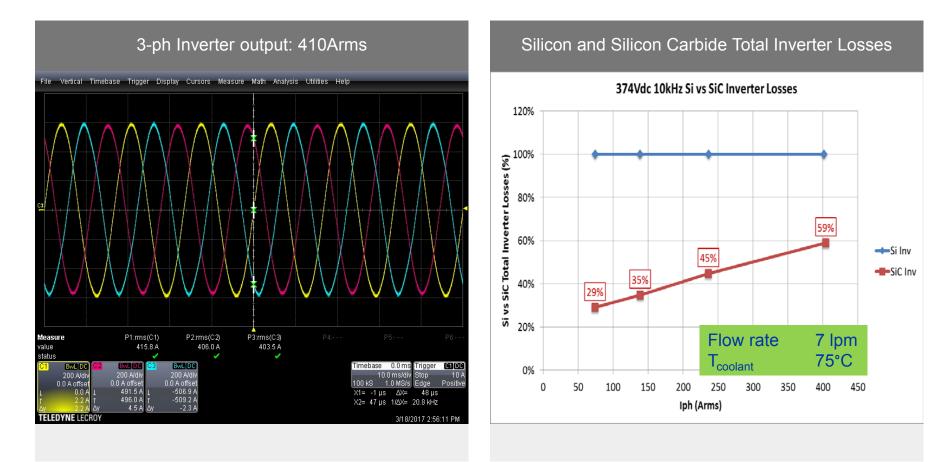

### Technical Accomplishments Inverter Losses Using 3-Phase Inductive Load

**SiC Inverter Performance**

### Responses to Previous Year Reviewers' Comments

• The project was started in 2016 and was not reviewed at the previous year's Annual Merit Review

# Collaboration and Coordination with Other Institutions

- Delphi -

- Semiconductor device floorplan

- Power semiconductor design, build and characterization

- Inverter design, build and characterization

- Device and power module pre-qualification testing

- Wolfspeed

- 650V SiC MOSFET design and layout

- Fabrication and characterization of the SiC MOSFET

- Pre-qualification testing at the die level

- Oak Ridge National Laboratory

- Inverter gate drive optimization

- Modeling of power module

# **Remaining Challenges and Barriers**

- Optimizing the design for cost and performance for high currents in the order of 650 900Arms is a challenge.

- Developing accurate cost models for the SiC based on realistic potential volumes is a challenge.

- Cost is potentially a barrier for some applications and may inhibit widespread adoption for some applications.

- Optimized gate drive perfromance is a challenge

- Sort Circuit Safe Operating Area is a concern

- Meeting EMC performance for automotive applications is a challenge due to the high switching speeds

# **Proposed Future Research**

- Continue build of Single Switch device

- Continue reliability testing at the die and package level

- Complete design of half-bridge semiconductor package

- Build and characterize half-bridge semiconductor package across temperature

- Complete second turn of inverter with half-bridge semiconductor package

- Optimization of gate drive for SiC half-bridge semiconductor module

- Quantify potential costs at significant SiC device modules for comparison to Si based IGBT and Diode traction drive inverter

Any proposed future work is subject to change based on funding levels.

# Summary

Single Switch Power Device and Packaging

- To date a dual side cooled 650V single switch power semiconductor device has been designed and fabricated

- 500Arms capability

- Die size 37mm<sup>2</sup>

- Mean Rdson ~7.7mΩ (at 75A, 25°C)

- Statically and dynamically test at the device and package level

- Thermal performance in heat rail has been characterized

- Tested in a dual side cooled traction inverter application configuration

- SiC inverter losses have been compared to state-of the art Si IGBT and Diode

Half-bridge Power Semiconductor Device and Packaging

• Device has been designed

# Thank You