#### Geothermal Technologies Program 2010 Peer Review

Energy Efficiency & Renewable Energy

Pressure sensor and Telemetry methods for measurement while drilling in geothermal wells May 19, 2010

This presentation does not contain any proprietary confidential, or otherwise restricted information.

Vinayak Tilak GE Global Research

High Temperature Tools and Sensors, Down-hole Pumps and Drilling

## Overview

Energy Efficiency & Renewable Energy

#### **Timelines**

- Project start date Dec 29, 2009

- Project end date Dec 28, 2012

- Percentage completed 0%

#### **Partners**

• Auburn University (Prof. Wayne Johnson) – high temperature electronics packaging Program Objective:

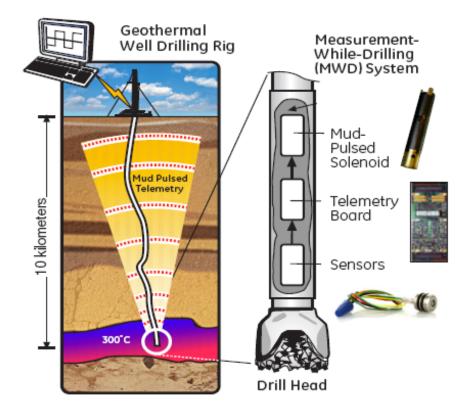

• Develop electronics for sensors and telemetry for measurement while geothermal drilling

U.S. DEPARTMENT OF

• Demonstrate multiple sensor systems multiplexed through a telemetry system

#### **Budget**

- Total budget \$4.3MM

- DOE share \$3.4MM

- GE share \$0.9 MM

- Funding planned for 2010 \$1.3MM

## GTP Barrier addressed by this technology

• Development of high temperature (300°C) logging tools and sensors to enable economic well construction and reservoir characterization

**ENERGY** Energy Efficiency & Renewable Energy

## **Project Objective**

Develop telemetry electronics and pressure sensor system for operation at 300°C and demonstrate the operation of multiple pressure sensor systems at 300°C

### **Benefits to Geothermal industry**

- Enable high temperature well construction MWD using this technology can enable economic drilling

- Better reservoir characterization through long term reservoir monitoring sensors based on this technology will be designed to operate at high temperatures for months

#### Key innovations

• Silicon carbide based digital and analog integrated circuits used for active electronics – The integrated circuits on silicon carbide attempted in this project will be the most complex till date

• Ceramic based packaging and board materials that are rated to operate at 300°C and with high shock and vibration specs – Traditional organic based boards and lead based solders are not used in this approach

## 2010 Objectives

- Demonstrate simple digital electronics complexity of shift registers on silicon carbide

- Design the sensor system architecture and telemetry module based on silicon carbide capability

- •Design and fabricate silicon carbide based analog electronics chip sets for pressure sensor system

- Define process for chip-level and board level packaging for 300°C operation while meeting the shock and vibration specification

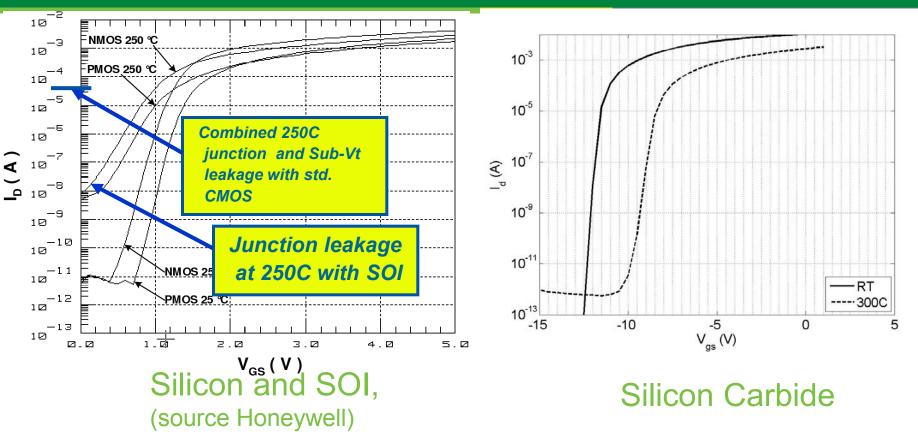

## Scientific Approach – Why SiC ?

U.S. DEPARTMENT OF

Energy Efficiency & Renewable Energy

The band gap of SiC (3.26 eV) compared to the band gap of Si (1.12eV) is the reason for the low leakage of p-n junctions at high temperatures

Objective: For optimum performance we want to have ratio of "ON' current to "Off" current

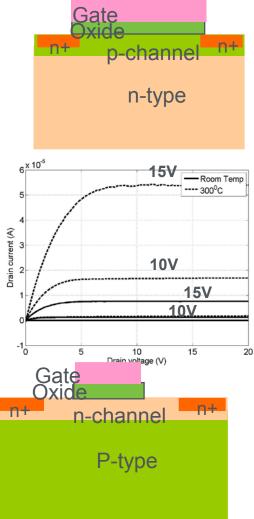

## Technical Approach – SiC MOSFETs

Energy Efficiency & Renewable Energy

#### **Enhancement-mode MOSFET**

- Normally off Efficient use of semiconductor real estate, ease of scaling

- P-MOS devices not ready for circuits and therefore NMOS logic is used

- Low mobility due to poor oxide carbide interface leads to poor performance, operate only in saturation region

- Threshold voltage temperature coefficient is much larger (~15 mV/°C) than in silicon devices (2 mV/ °C) making analog design more complicated

- Current increases with increasing temperature conventional silicon modeling tools cannot be used

- Load resistor may have a different temperature coefficient compared to the drive transistor

#### **Depletion-mode MOSFET**

- Normally on inefficient use of real estate

- Low Efield intensity in drain region Higher reliability of gate oxide

- High mobility of channel electrons and can be operated in linear region

Energy Efficiency & Renewable Energy

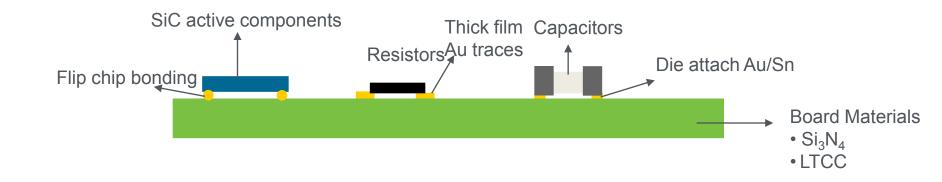

- Passives to be sourced from vendors

- SiN/LTCC substrate to be used as the electronics board substrate to minimize Coefficient of thermal expansion (CTE) mismatch between SiC and substrate.

- Au thick film for gold traces explore multi layers

- AuSn is the preferred attach material for passives

- Au Flip chip bonding bonding for electrical connections

| Mechanical Test      | Specification                                                |

|----------------------|--------------------------------------------------------------|

| Sine Sweep Vibration | 30G, 10-2000Hz, each axius                                   |

| Random Vibration     | 20Grms, 10-80Hz 6dB/oct, 80-<br>1000Hz flat, 4 hrs each axis |

| Mechanical Shock     | 1000G, 1mSec, ½ sine pulse,<br>each axis                     |

Test conditions for shock and vibration testing

## Accomplishments – Device models

U.S. DEPARTMENT OF

Energy Efficiency & Renewable Energy

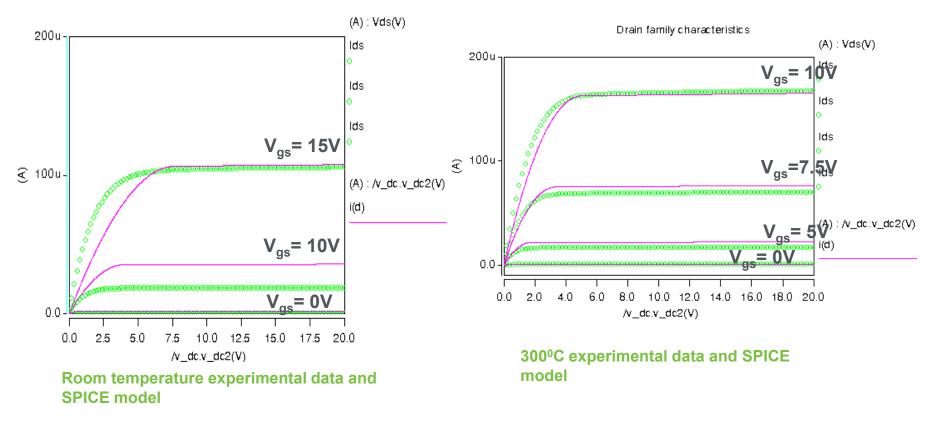

- We have developed a temperature independent level 2 SPICE model for use at room temperature and 300°C need to ensure that the circuit works with two different models

- Plan to build a temperature dependence in the model Dec 2010

## Accomplishments - Planned

U.S. DEPARTMENT OF

Energy Efficiency & Renewable Energy

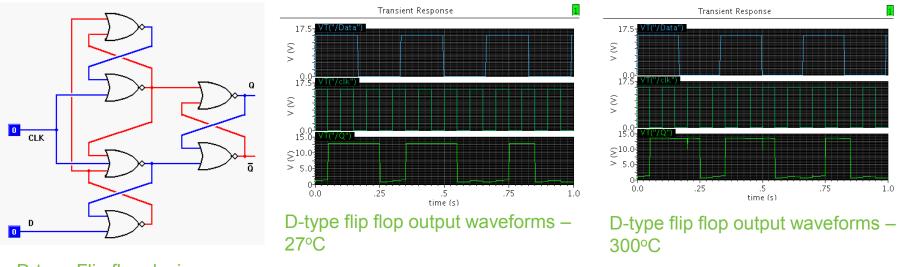

D-type Flip flop design

• Circuit design for simple gates, combinatorial logic and shift registers to be completed – June 2010

- Fabricate and test ICs September 2010

- Sensor and telemetry architecture preliminary design August 2010

- Pressure sensor electronics design and fab September 2010

## Project Management – Gantt chart

U.S. DEPARTMENT OF

Energy Efficiency & Renewable Energy

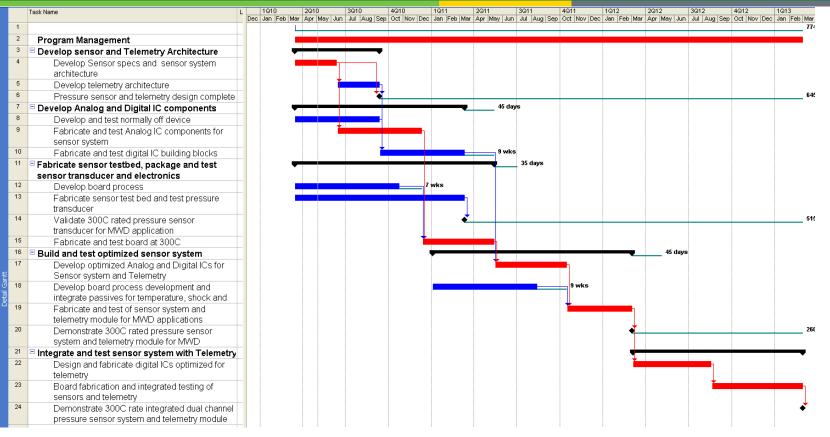

#### FY 2010 milestones – Planned spend \$1.3MM

- Complete pressure sensor and telemetry module design September 2010

- Demonstrate simple SiC digital ICs at 300°C October 2010

- Validate pressure sensor transducer for MWD operation at 300°C November 2010

- Develop board level packaging process for 300°C October 2010

# Project management – FY 2011, 2012 milestones

Energy Efficiency & Renewable Energy

#### FY 2011 milestones – Planned spend \$1.5MM

- Fabricate and test at 300°C chip set for pressure sensor system March 2011

- Fabricate and test at 300°C board for pressure sensor system May 2011

- Fabricate and test chip set for telemetry module May 2011

- Fabricate and test at 300°C chip set for telemetry module June 2011

- Fabricate board and test at 300°C board for telemetry module August 2011

#### FY 2012 milestones – Planned spend \$1.5MM

• Fabricate and test optimized chipset for 300°C pressure sensor system and telemetry module – March 2012

• Fabricate and test at 300°C integrated pressure sensor systems and telemetry module – August 2012

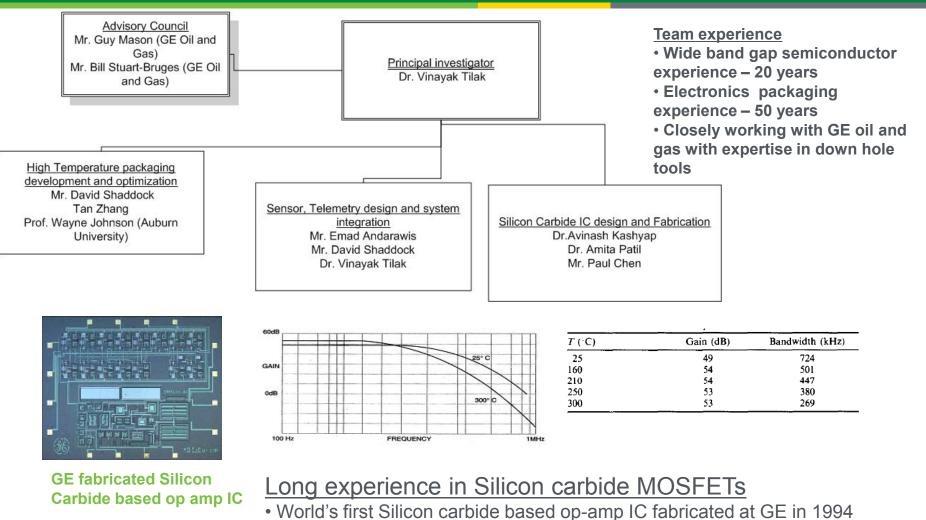

## Program management - Team

**ENERGY** Energy Efficiency & Renewable Energy

• Current active program that has demonstrated a 1.2 kV, 30 Amp SiC MOSFET with world record on resistance of 7 m $\Omega$ -cm<sup>2</sup>

**ENERGY** Energy Efficiency & Renewable Energy

- FY 2010 digital building block chips demonstrated, analog sensor system chips fabricated, board process for 300°C shock and vibration specs identified

- FY 2011 digital telemetry board fabricated, analog board fabricated and tested individually

- FY 2012 all pieces of electronics demonstrated working in consort

- Future research

- Gamma at 300°C

- Field test of the electronics and sensor system

- Most complex digital electronics on SiC to be attempted

if successful, we will open > 300°C temperature regime

for electronics

- Packaging that meets both temperature, shock and vibration specifications

- Boards that operate at 300°C, 30 g vibration and 1000 g shock to be demonstrated

- Electronics should enable the transmission of multisensor data to the surface using a mud pulse solenoid

Energy Efficiency & Renewable Energy

## **Supplemental Slides**

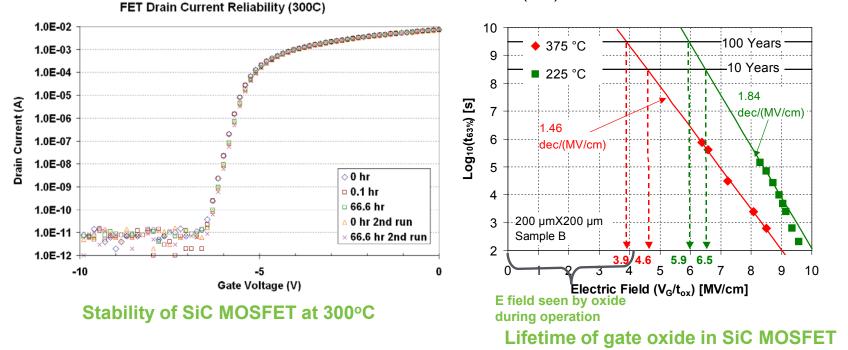

## Scientific Approach – Gate oxidation

Data from L.C. Yu et al., "Oxide Reliability of SiC MOS Devices", IEEE International Integrated Reliability Workshop Final Report, pp. 141-144 (2008)

U.S. DEPARTMENT OF

Energy Efficiency & Renewable Energy

- NO based post oxidation anneals used to fabricate all the gate oxides in the project

- Reliability of gate oxide has improved at high temperature to MTTF of 100 years at 375°C

- Stability of SiC MOSFET after 132 hours at 300°C is a dramatic improvement on pervious generation MOSFETs

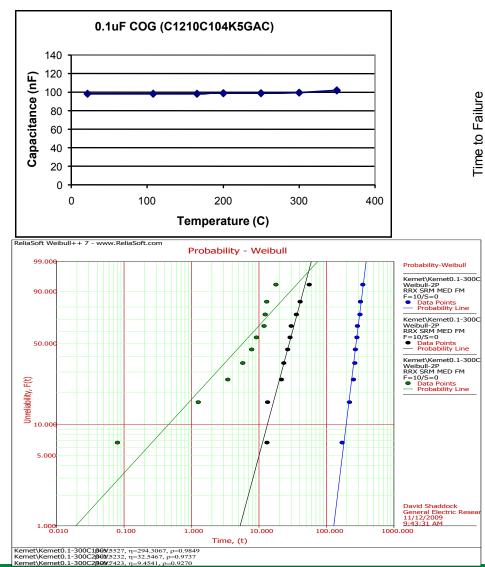

## Scientific approach - capacitors

U.S. DEPARTMENT OF

Energy Efficiency & Renewable Energy

Value: 0.10uF, 50V, H dielectric Temperature: 300C Voltage Bias: 290, 200, 100 Model parameters: n=3.67 using 100 and 200V Estimated Life: 17254 hrs at 25V <u>Work performed for the DOE</u> <u>Geothermal Technologies Program</u> under DE-FG-GO3608GO18181

17 | US DOE Geothermal Program

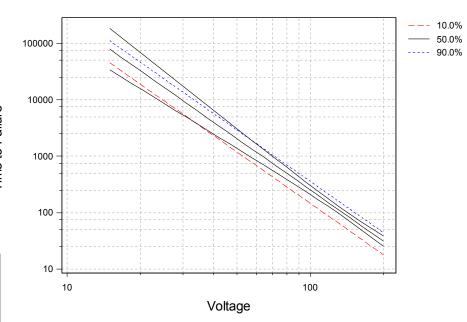

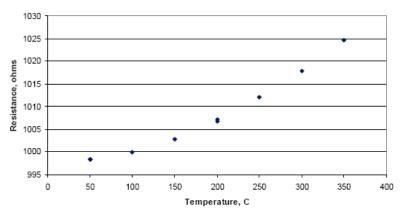

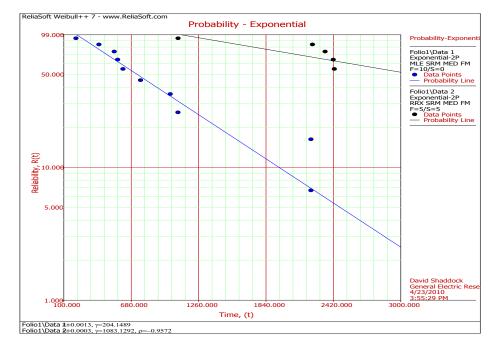

## **Scientific Approach - Resistors**

U.S. DEPARTMENT OF

Energy Efficiency & Renewable Energy

1 k $\Omega$  thick film resistor

Mean life 962.3558 hours @ 1 % degradation 3994.9697 hours @ 2% degradation

# Temp=350C, 16V across DUT, 0.25W (at rating) 3529 hrs, 7 failures

<u>Work performed for the DOE</u> <u>Geothermal Technologies Program</u> <u>under DE-FG-GO3608GO18181</u>